Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

All Platypus eFPGA hardened IP cores are backed up by an open architecture guarantee.

Overview

All Platypus eFPGA hardened IP cores are backed up by an open architecture guarantee. Complete machine readable descriptions of standard architectures can be found in the Logiklib open source repository.

Parametrized soft RTL logic wrap the hardened IP core to handle reset, boot-up, security, and bitstream loading. Bitstream programming is done via a standardize memory mapped register interfaces (APB, AXI-Lite, or UMI) selectable by the user during design integration.

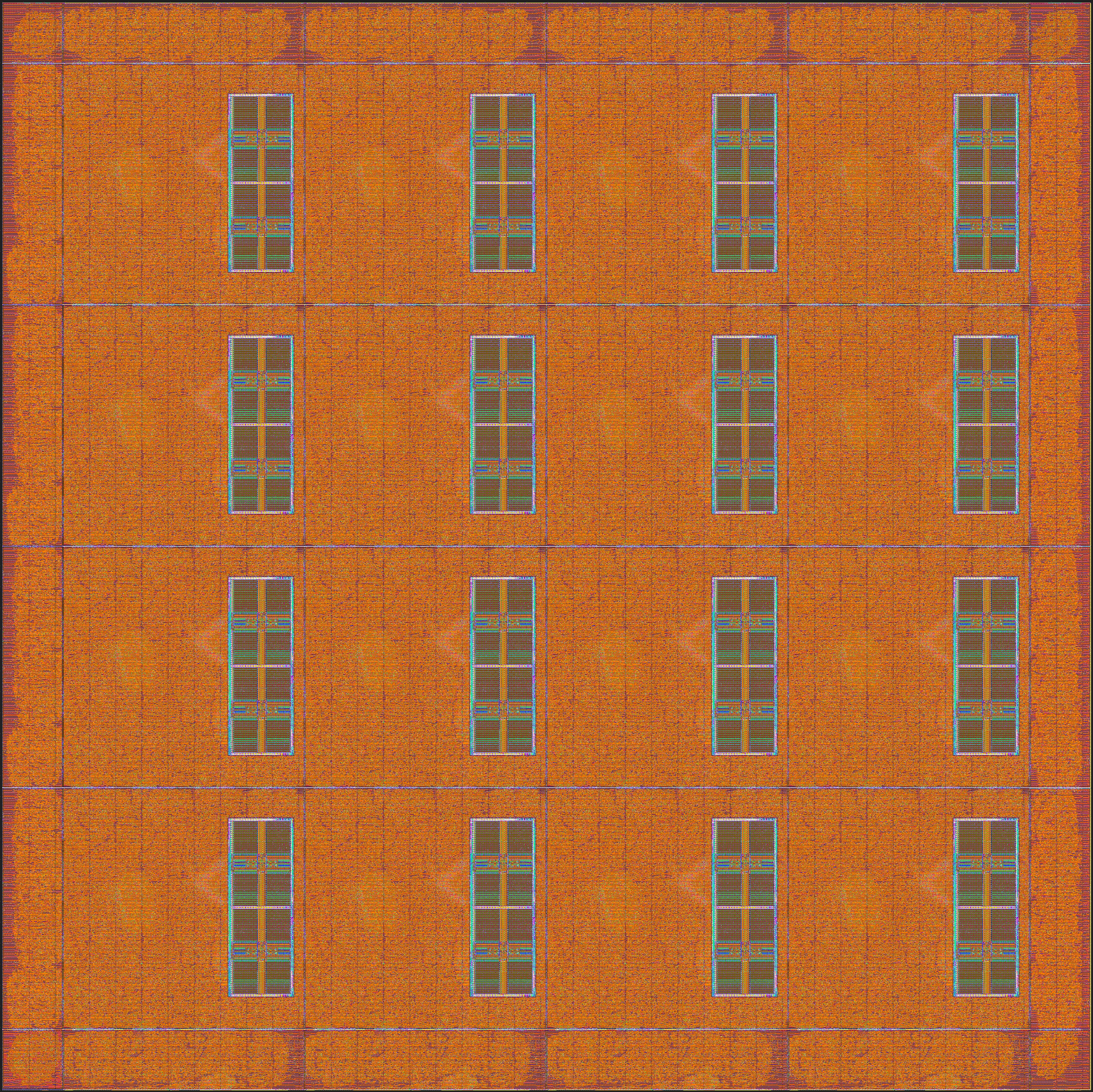

An experimental Z1010 heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs has been ported to the GlobalFoundries GF12LP process. The picture below shows the full layout of the experimental architecture. The official Z1010 standard will include a different ratio of LUTs, DSPs, and BRAM.

| Process | LUTs | Regs | I/O | DSPs | BRAM | Width | Height |

|---|---|---|---|---|---|---|---|

| GF12LP | 512 | 512 | 1,024 | 16 | 1Mb | 1036.8um | 1037.2um |

Block Diagram

Benefits

- 100% open and standardized FPGA architectures

- 100% open source FPGA bitstream formats

- 100% open source FPGA development tools

Applications

- FPGA/CPLD/ASIC obsolescence

- hardware security

- I/O peripherals

- interface bridges

- motor control

- signal muxing

- power management

- glue logic

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 12nm | LP | — |

Specifications

Identity

Provider

Learn more about eFPGA IP core

Tapeout Predictability with Hardened eFPGA IP Blocks

Accreditation Without Compromise: Making eFPGA Assurable for Decades

Silicon Insurance: Why eFPGA is Cheaper Than a Respin

Integrating eFPGA for Hybrid Signal Processing Architectures

Epson Achieves 50% Energy Efficiency with QuickLogic eFPGA

Frequently asked questions about eFPGA IP cores

What is Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP?

Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP is a eFPGA IP core from Zero ASIC listed on Semi IP Hub. It is listed with support for globalfoundries.

How should engineers evaluate this eFPGA?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this eFPGA IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.