eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

RapidFlex eFPGA IP provides a reconfigurable, upgradeable, and iterative logic computing layer for SoCs, MCUs, AI accelerators, i…

Overview

RapidFlex eFPGA IP provides a reconfigurable, upgradeable, and iterative logic computing layer for SoCs, MCUs, AI accelerators, industrial control, and communication chips. Based on RapidFlex's self-developed ArkAngel® toolchain (AAEE), our eFPGA core delivers full-flow capabilities from architecture exploration → RTL → physical implementation (GDSII) → digital design flow verification, leading the industry in performance density, integrability, and toolchain experience.

Key features

High-Performance Logic Fabric (LUT / FF / DSP-lite / BRAM)

- Configurable logic scale from thousands to millions of LUTs

- Supports high-density distributed memory

- Flexible combination of LUT, FF, DSP-lite, and BRAM with extremely low power consumption

- Ideal for control and protocol, bit-level, and streaming processing scenarios

Ultra-Lightweight, Easy-to-Integrate SoC-Level Interface

- Supports standard buses such as AXI, AHB, APB

- Flexible I/O planning for seamless integration with packaging/testing

- Supports low-power, sleep/retention, and low-power wake-up logic

Full-Flow IP Core Delivery from RTL → GDSII

We provide digital verification capabilities compliant with mainstream ASIC tape-out processes, including:

- Logic Synthesis with Automatic QoR Tuning

- Multi-objective optimization for performance/area/power

- Quantifiable PPA convergence based on process libraries

- Floorplan & Placement Support

- Partitioning/sub-array planning for eFPGA fabric

- Definition of boundary cells, channels, and high-level routing structures

- Routing & Congestion Optimization

- Local structural optimization based on routability prediction

- AI-assisted congestion inference (ArkAngel® AE model)

- Static Timing Analysis (STA)

- Full-flow verification of setup/hold/clock gating

- Multi-corner / multi-mode analysis

- Power Analysis

- Dynamic/static power estimation

- Fabric activity factor scanning

- Physical Verification (DRC / LVS)

- Complete layout design rule checking

- Compatible with mainstream processes (SMIC / TSMC / etc.)

Customers can choose according to project needs:

- Soft IP: Flexible architecture and scale adjustments

- Hard IP: Fixed layout, guaranteed performance, ready for tape-out

This capability has been successfully validated on mainstream process nodes such as SMIC 40nm and TSMC 22nm.

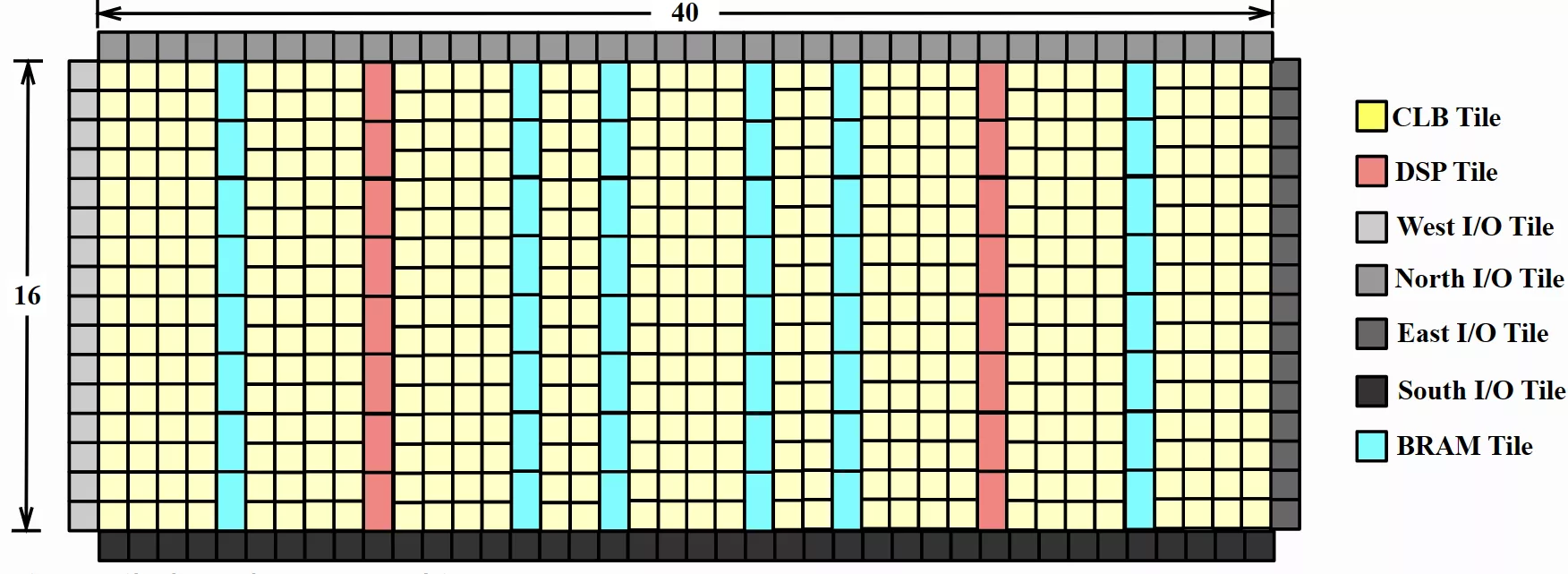

Block Diagram

Applications

RapidFlex eFPGA IP has demonstrated its reconfigurable value across various industry scenarios:

1. Motor Control — Domestic Alternative to TI C2000

- Implements fast programmable PWM, dead-time control, overcurrent/overvoltage protection

- Migrates motor algorithms/digital control logic to reconfigurable fabric

- Offers significant flexibility in industrial servo, elevator, power tools, and EV controllers

2. Lightweight PSoC (Similar to Cypress/Infineon)

- eFPGA as Smart IO / programmable logic peripheral / UDB (Universal Digital Block)

- Implements GPIO matrix, reconfigurable serial interfaces, PWM modules, etc.

- Suitable for PMIC, IoT MCU, and sensor integration chips

3. Edge AI Lightweight Acceleration (Sensor Arrays)

- Event-driven logic / feature extraction / bit-level preprocessing

- Upgradeable and modifiable CNN front-end processing modules

- Applied in smart security, low-power sensor hubs, and AIoT

4. High-End RF / Communication Chips

- Reconfigurable protocol stack: NR/5G, WiFi, private network communication

- Upgradable frame parsing, CRC, and scheduling logic with protocol updates

- Provides rapid revision capability to adapt to regional standards

5. Image Signal Processing (ISP)

- Sensor interface processing (MIPI, DVP)

- Denoising, HDR synthesis, Gamma, auto-exposure auxiliary logic

- Used in smart cameras, automotive imaging, and industrial vision

6. Smart NIC / SmartNIC

- Reconfigurable flow tables, flow steering, ACL / L4-L7 parsing

- Customizable security acceleration, encryption/decryption, packet classification

- Deep collaboration with DPU/CPU to meet cloud and data center demands

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about eFPGA IP core

Tapeout Predictability with Hardened eFPGA IP Blocks

Accreditation Without Compromise: Making eFPGA Assurable for Decades

Silicon Insurance: Why eFPGA is Cheaper Than a Respin

Integrating eFPGA for Hybrid Signal Processing Architectures

Epson Achieves 50% Energy Efficiency with QuickLogic eFPGA

Frequently asked questions about eFPGA IP cores

What is eFPGA IP — Flexible Reconfigurable Logic Acceleration Core?

eFPGA IP — Flexible Reconfigurable Logic Acceleration Core is a eFPGA IP core from Rapid Flex listed on Semi IP Hub.

How should engineers evaluate this eFPGA?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this eFPGA IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.