Embedded FPGA

SPC (Synthesizable Programmable Core) is a soft FPGA core that is fully integrated into standard design flows and that allows the…

Overview

SPC (Synthesizable Programmable Core) is a soft FPGA core that is fully integrated into standard design flows and that allows the seamless implementation of generic RTL programmable logic in ASICs and SOCs.

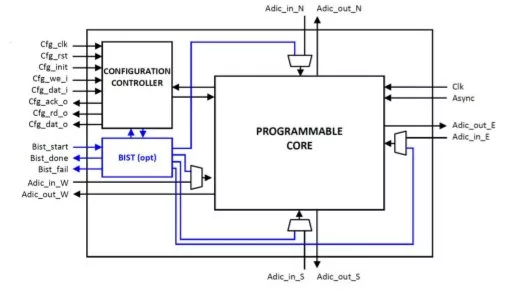

The IP contains three modules:

- A Look Up Table (LUT) based programmable core, or FPGA, suitable for mapping generic RTL functions.

- A configuration controller for the interaction between SOC and FPGA system functions such as the loading/checking of the bitstream.

- A Built-In Self-Test for industrial grade manufacturing testing or in-system self-testing.

Key features

- Configuration

- Control interface.

- On the fly bitstream decompression and decryption.

- High granularity partial reconfiguration.

- Test

- ATPG compatibility.

- BIST engine.

- Test vectors for manufacturing.

- Alpha scrubbing.

- CRC/ECC

- Compilation Tool

- RTL to bitstream synthesis.

- Effort and/or Timing driven place and route.

- TCL shell for flexible use and integration into 3rd party software.

Block Diagram

Benefits

- Fully integrated into RTL SOC design flow:

- SPC IP RTL/gate simulation.

- Accurate Timing Analysis.

- No black box (LEF/GDSII).

- No verification gap.

- Highly scalable and customizable:

- Pre-existing SPC blocks or

- Custom size SPC blocks.

- 100 to 100k LUTs.

- Multiple SPC’s per chip.

- SPC LUT count is defined with single digit precision to optimize area.

- Technology independent:

- Any CMOS node with digital capacity:

- CMOS 180nm – 14nm

- SOI Rad-Hard

- Any foundry.

- Days/Weeks to deliver.

- Any CMOS node with digital capacity:

- No FPGA background required.

- One-time fee to use compilation tools.

- Independent FPGA technology:

- SPC does not copy proprietary commercial FPGA structures (Logic Elements, LUTs, BitRAMs, DSPs …).

- SPC does not rely on commercial FPGA software or third party software, although it is possible to use them.

- ADICSYS’ FPGA software:

- Linux support for ASIC integration.

- Distributable for Linux and Windows end users.

- Compilation Runtime, RTL to bitstream:

- 10k Gates per minute.

- 2X to 4X higher density than competing blocks

What’s Included?

- SPC IP comprising:

- Synthesizable RTL.

- Bitstream Loader.

- BIST.

- Synthesis, simulation and STA scripts.

- Place and route scripts and manual.

- Possibility to deliver GDSII in parallel.

- Test patterns.

- ADICSYS FPGA compilation software:

- RTL Parser.

- Synthesis.

- FPGA place & route.

- FPGA bitstream generation.

- Embeddable TCL control shell.

- Operating systems:

- Linux starting with RHEL4.

- Windows starting with XP.

- Documentation, Examples, Training.

- Early SOC definition support.

- General ASIC design assistance.

- SPC customization.

- Standalone FPGA design assistance.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about eFPGA IP core

Tapeout Predictability with Hardened eFPGA IP Blocks

Accreditation Without Compromise: Making eFPGA Assurable for Decades

Silicon Insurance: Why eFPGA is Cheaper Than a Respin

Integrating eFPGA for Hybrid Signal Processing Architectures

Epson Achieves 50% Energy Efficiency with QuickLogic eFPGA

Frequently asked questions about eFPGA IP cores

What is Embedded FPGA?

Embedded FPGA is a eFPGA IP core from ADICSYS listed on Semi IP Hub.

How should engineers evaluate this eFPGA?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this eFPGA IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.