General Purpose PLL for VIS 150nm

The OT3122v150 is a flexible clock multiplier PLL function with a wide range of input and output frequencies and is designed for …

Overview

The OT3122v150 is a flexible clock multiplier PLL function with a wide range of input and output frequencies and is designed for the VIS 0.15µ digital, mixed signal, or high voltage CMOS processes. The design features an advanced multi-stage balanced VCO for exceptional cycle to cycle jitter performance.

This function is also available for TSMC 130nm, TSMC 152nm, TSMC 180nm, IBM 180nm, and ams 180nm.

Key features

- Wide range N, M, P integer dividers.

- 40MHz – 600MHz output frequency range.

- Comparable frequency range 8MHz – 50MHz.

- 18pS RMS cycle to cycle jitter at 600MHz.

- Lock-detect function.

- Bypass function.

- Well defined startup behavior.

- -40°C to 140°C temperature operation.

- Available divider selection program.

- Small cell area: 0.06mm2 in 0.18µ CMOS.

- 1.5mW typical power dissipation.

- 1.8V digital and analog supplies.

- 0.18µ CMOS process compatibility.

- Only 1.8V transistors are used in the design.

- Silicon proven.

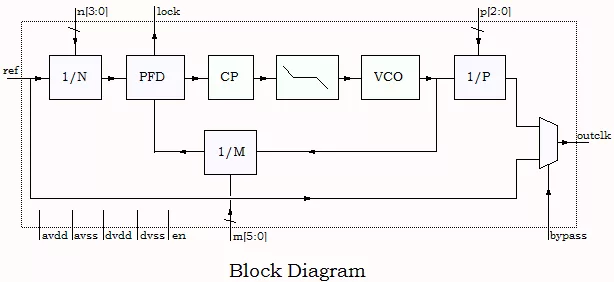

Block Diagram

Applications

- Crystal frequency to device internal clock multiplicatiion.

- Communication cores.

- Bus Interface cores.

What’s Included?

- Verilog model.

- CDL netlist for LVS.

- Design review documentation.

- GDS format layout.

- Timing files.

- Integration notes.

- Production test notes.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| VIS | 150nm | 150nm 1500 nm | Silicon Proven |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

- Founded 1995

- Privately owned consulting company

- Diversified customer base

- Self funded

- Early delivery of front-end models.

- On-site support available, including transfer of source to your design environment.

- Available on-site design review.

- On-site training for source licensing.

- Option to take ip though your own quality and review processes.

- Characterization support.

- Fast and flexible legal. We typically accept your standard bi-directional NDA.

- Simple plain-language contracts.

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is General Purpose PLL for VIS 150nm?

General Purpose PLL for VIS 150nm is a PLL IP core from Obsidian Technology listed on Semi IP Hub. It is listed with support for vis Silicon Proven.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.