16 to 64 MHz Phase-Locked Loop

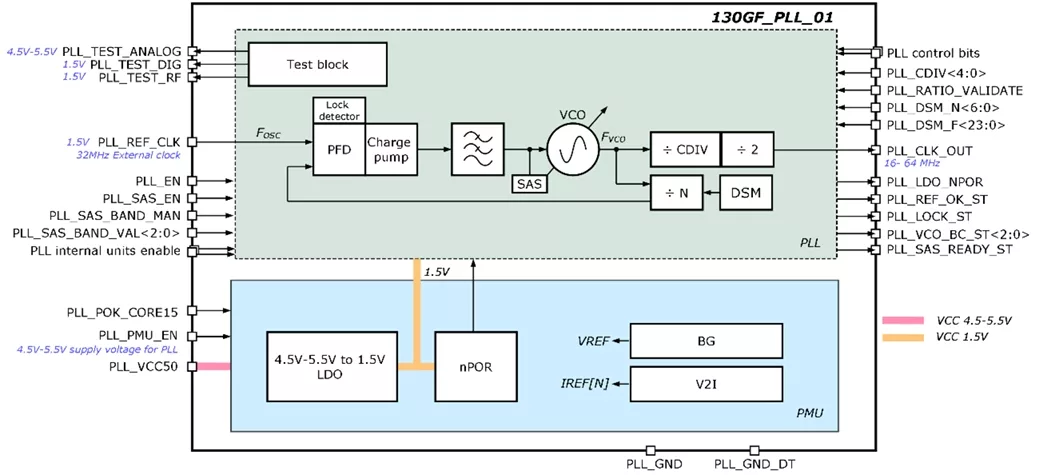

130GF_PLL_01 is a ring VCO based phase-locked loop frequency with 16-64 MHz CMOS compatible output clock and fine frequency resol…

Overview

130GF_PLL_01 is a ring VCO based phase-locked loop frequency with 16-64 MHz CMOS compatible output clock and fine frequency resolution thanks to the embedded delta-sigma modulator (DSM). The IP consists of a ring voltage controlled oscillator (VCO) with multiple sub-bands and sub-band autoselection system (SAS), a programmable N feedback divider (÷N) controlled by DSM, a digital phase-frequency detector (PFD) with a lock detector (LD), a charge pump (CP) with internal loop filter, a power management unit (PMU), and a programmable C clock divider (÷C).

Key features

- Global Foundries BCD 130 nm

- Power supply from 4.5 to 5.5 V

- Operating temperature -40…+125 °C

- Low current consumption: up to 1 mA

- Reference frequency 32 MHz

- Output frequency from 16 to 64 MHz

- RMS jitter less than 35 ps

- PLL area 0.2 mm2

Block Diagram

Applications

- Digital circuit clocking

- Clock for analog sensors

What’s Included?

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 130nm | 130 1300 nm | Silicon Proven |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is 16 to 64 MHz Phase-Locked Loop?

16 to 64 MHz Phase-Locked Loop is a PLL IP core from NTLab listed on Semi IP Hub. It is listed with support for globalfoundries Silicon Proven.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.