Ethernet TSN MAC 10M/100M/1G/2.5G

Silicon agnostic Ethernet TSN MAC IP, IEEE 802.3 Ethernet Layer 2 solution with support for key TSN features The TSN MAC 10M/100M…

Overview

Silicon agnostic Ethernet TSN MAC IP, IEEE 802.3 Ethernet Layer 2 solution with support for key TSN features

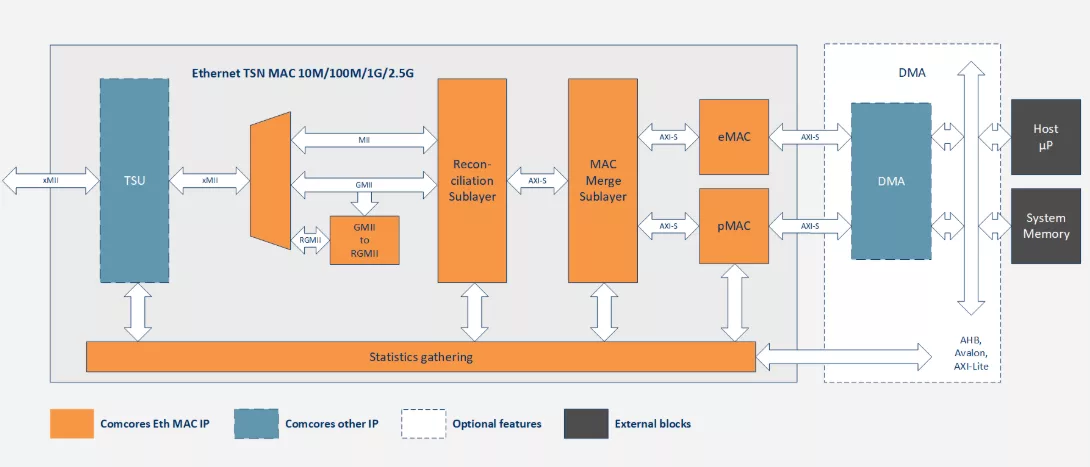

The TSN MAC 10M/100M/1G/2.5G provides a complete IEEE 802.3 Ethernet Layer 2 solution with support for key TSN features including 802.1Qbu Pre-emption, 802.3br Interspersing Express Traffic, and optionally 802.1AS Timing and Synchronization and 802.1Qbv Enhancements for Scheduled Traffic. The TSN MAC enables deterministic low latency and guaranteed jitter for time sensitive applications. The TSN MAC allows flexibility in selecting a subset of standards depending on your application from industrial to automotive.

The feature rich MAC core is a low latency cut-through implementation, while keeping size at a minimum. The core is fully configurable and can optionally include IEEE 1588 Timestamping Unit (TSU). The Ethernet MAC Core has a standard GMII interface on the PHY side, with MII and RGMII being optional.

Key features

Delivers Performance

- Designed to IEEE 802.3-2018 specification

- Qbv and AS extensions are available

- Low latency and compact implementation

- Full duplex Ethernet interfaces

Feature Rich

- FCS generation supported

- Supports Link verification

- Jumbo frames

- Independent TX and RX Maximum Transmission Unit (MTU) frame length

- Optionally comprehensive statistics gathering

- Easy integration with standard AXI4 lite or APB

- IEEE 802.3br (Interspersing Express Traffic) Supported

- IEEE 802.1Qbu (Frame Preemption) supported

- IEEE 802.1CM (Time-Sensitive Networking for Fronthaul) supported

- Energy Efficient Ethernet

- IEEE 802.1Qbv (Enhancements for scheduled traffic).

- IEEE 802.1CB (Frame Replication and Elimination for Reliability).

- IEEE 802.1AS (Timing and Synchronization).

- IEEE 1588 (Precision Time Protocol, PTP).

Highly Configurable

- TSN features can be enabled/disabled independently

- Cut-through support

Silicon Agnostic

- Designed in SystemVerilog and targeting both ASICs and FPGAs

Block Diagram

What’s Included?

The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note

- Simulation Environment, including Simple Testbed, Test case and Test Script

- Programming Register Specification

- Timing Constraints in Synopsys SDC format

- Access to support system and direct support from Comcores Engineers

- Synopsys SGDC Files (optional)

- Synopsys Lint, CDC and Waivers (optional)

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Ethernet TSN MAC 10M/100M/1G/2.5G?

Ethernet TSN MAC 10M/100M/1G/2.5G is a Ethernet IP core from Comcores listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.