10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface

The GRETH_GBIT core implements a 10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface.

Overview

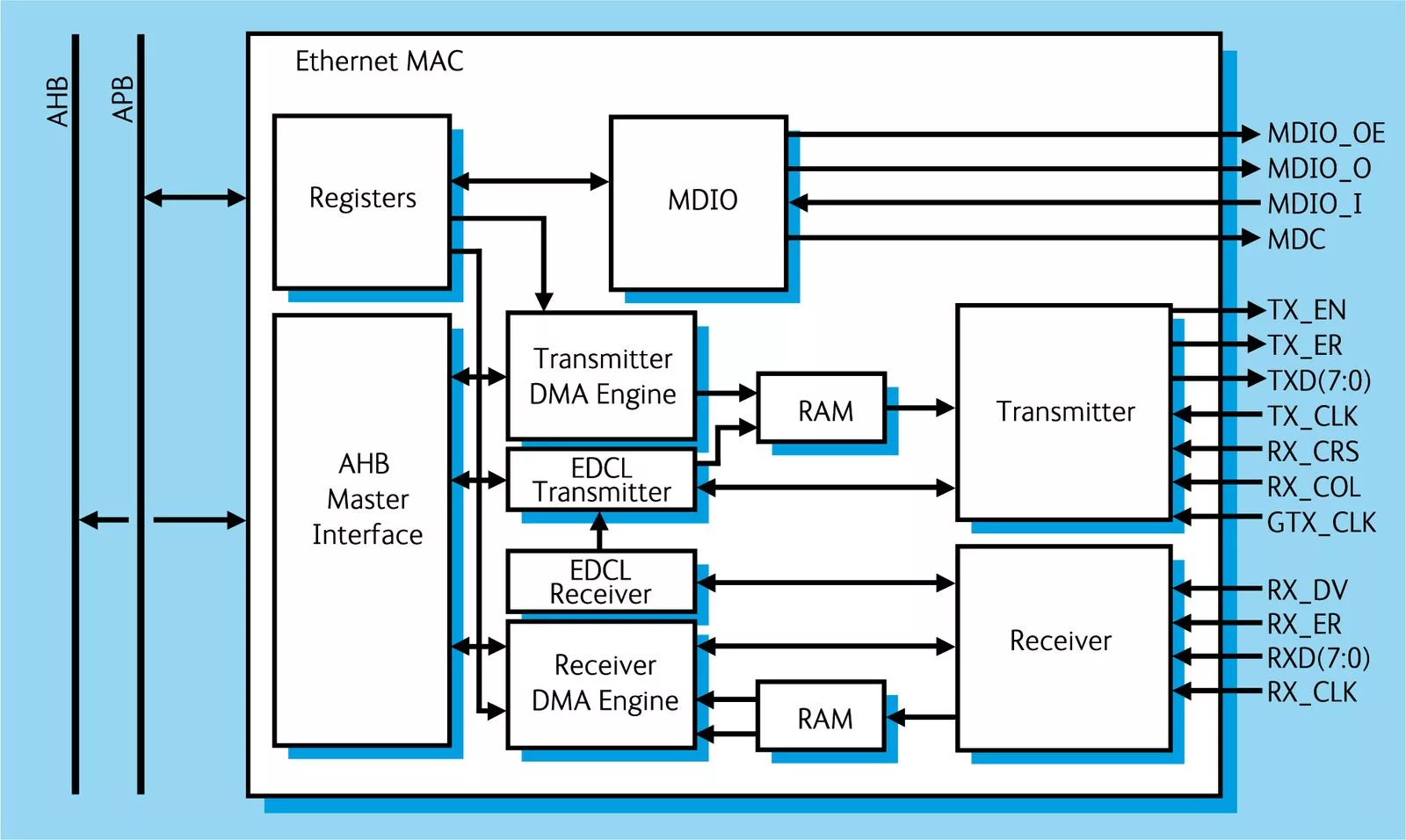

The GRETH_GBIT core implements a 10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface. Receive and transmit data is autonomously transferred between the Ethernet MAC and the AMBA AHB bus using DMA transfers.

Key features

- AMBA AHB back end with DMA

- Support for Scatter/Gather DMA

- Checksum offloading in hardware for TCP/IP/UDP for both receiver and transmitter

- Descriptor based autonomous multi-packet transfer

- Portable

Block Diagram

Benefits

- Easily integrated through AMBA plug&play

- Low-area overhead

- Free device drivers

What’s Included?

- VHDL source code or FPGA/ASIC netlist

- Stand-alone testbench

- Optional plug and play interface for GRLIB IP-library

- User's manual

- Drivers for VxWorks and available open source for RTEMS and Linux

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is 10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface?

10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface is a Ethernet IP core from Frontgrade Gaisler listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.