Ethernet 10/100 PHY

The KA13ETHB33 is a single-port PHY with an MII (Media Independent Interface).

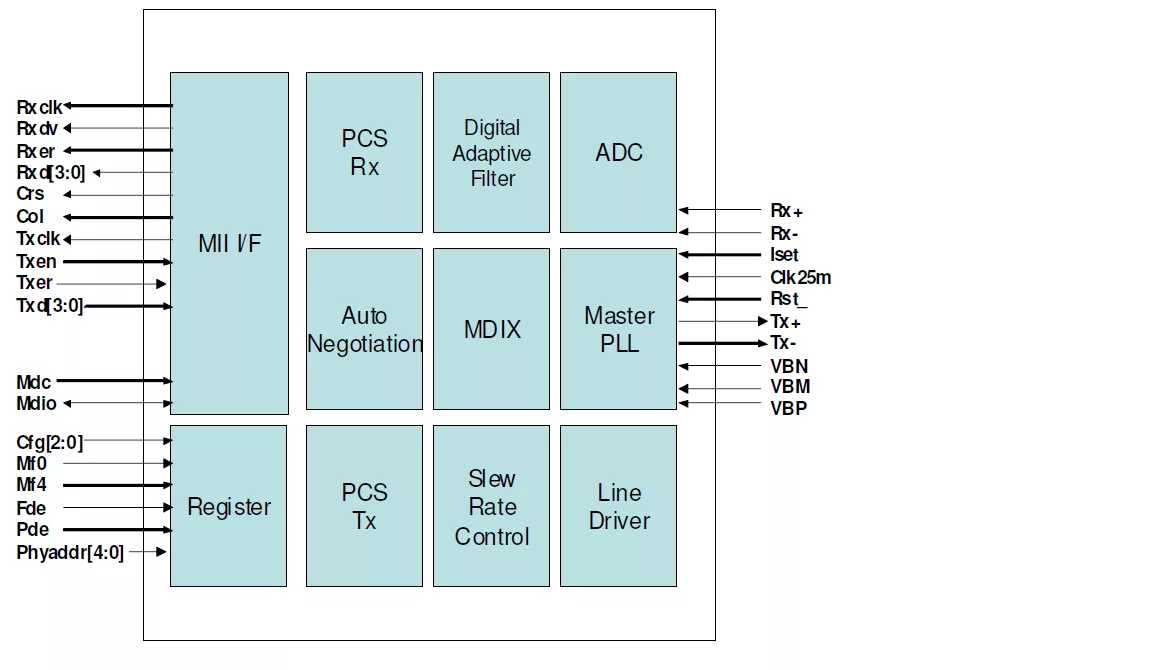

Overview

The KA13ETHB33 is a single-port PHY with an MII (Media Independent Interface). It implements all 10/100M Ethernet Physical- layer functions including the Physical Coding Sub-layer (PCS), Physical Medium Attachment (PMA), Twisted Pair Physical Medium Dependent sub-layer (TP-PMD), 10Base-Tx Encoder/Decoder, and Twisted Pair Media Access Unit (TPMAU).

Key features

- Supports MII.

- Auto-MDX

- 10/100Mbs operation supported

- Full/half duplex operation

- Twisted pair output only

- Supports Base Line Wander (BLW) compensation

- Adaptive Equalization

- 25MHz crystal/oscillator as clock source

- IEEE 802.3/802.3u compliant including auto- negotiation

- 0~125°C junction temperature

- Silterra 130nm CMOS process

Block Diagram

Benefits

- With on-chip DSP (Digital Signal Processing) technology, the chip provides excellent performance under all operating conditions.

Applications

- Network Interface Adapters

- Ethernet Hubs/Switches

- ADSL/Cable Modems

- VoIP Phone Sets

What’s Included?

- Data Sheet

- Test Documentation

- Integration Guide

- GDSII

- LVS netlist

- LEF model

- Verilog Model

- Timing Model

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is Ethernet 10/100 PHY?

Ethernet 10/100 PHY is a Single-Protocol PHY IP core from Key ASIC listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.