Overview

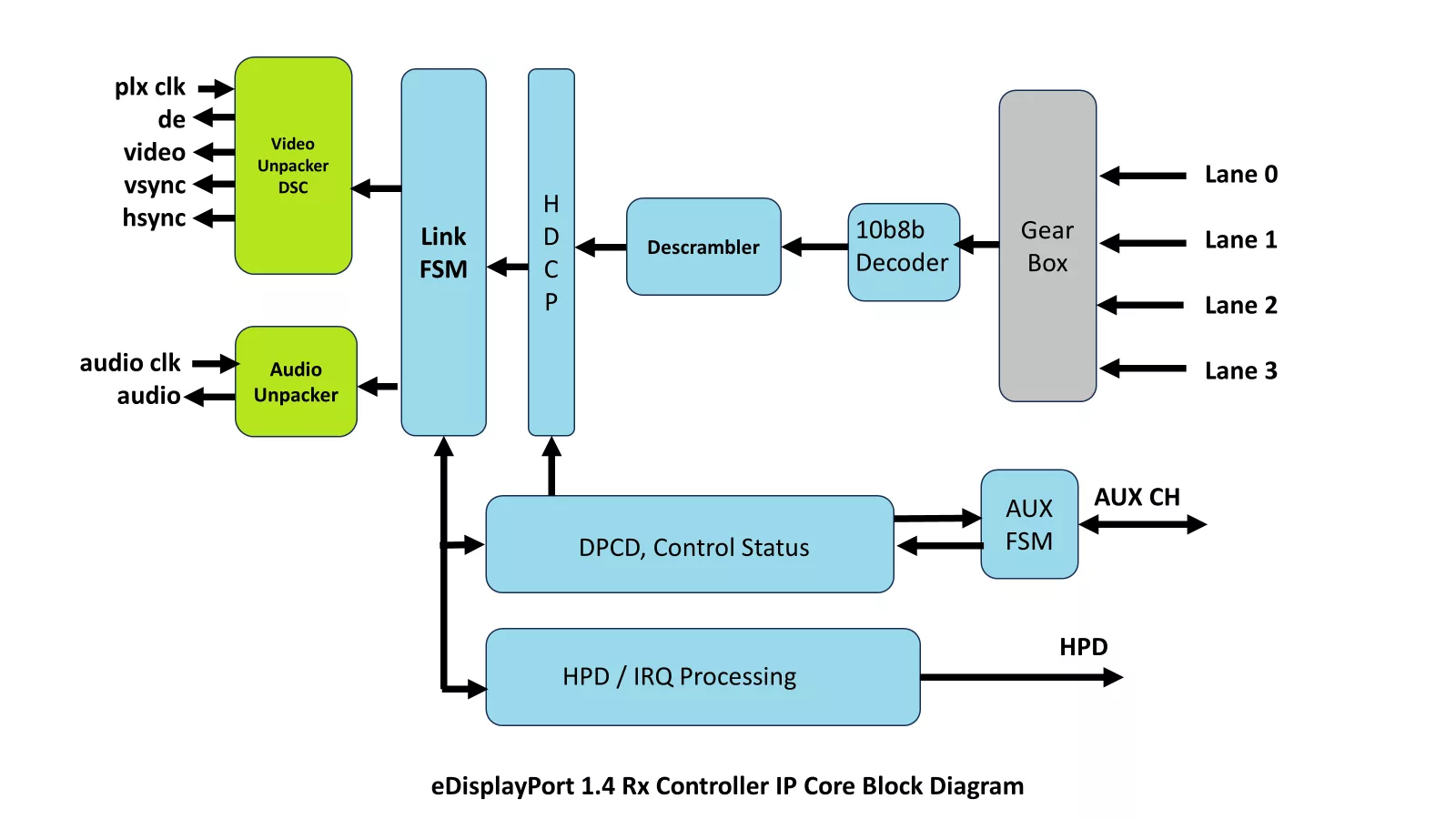

This eDisplayPort 1.4 Rx Controller IP Core is a versatile and comprehensive solution designed for easy integration into any SoC or FPGA development. It supports the eDP 1.4b specification and can be implemented in any technology, making it highly adaptable for various design needs. With a wide range of host bus interfaces, including AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone, or custom buses, it seamlessly integrates into any design architecture. Delivered in Verilog RTL, the eDP Receiver IP Core can be implemented in either ASIC or FPGA, offering flexibility in hardware choices. The IP has been validated using FPGA, ensuring its reliability and performance in real-world scenarios. The comprehensive package includes RTL code, test scripts, and a test environment for streamlined simulation. This eDisplayPort Rx IP Core is a feature-rich, user-friendly, and synthesizable design that empowers developers to effortlessly integrate it into their SoC or FPGA projects. With its support for eDP 1.4b, compatibility with various host bus interfaces, and flexible implementation options, it provides a robust solution for high-quality video and audio reception in electronic devices.

Provider

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about Displayport IP core

As automotive displays become part of the safety surface, traditional host-dependent display architectures are showing their limits. In this article, Trilinear outlines how a RISC-V supervised DisplayPort subsystem can provide isolated control, deterministic fault handling, and a more auditable architecture for advanced automotive display platforms.

In a computer system, both the GPU as well as the monitor have a certain rate at which they render or update an image, respectively. The rate is nothing but the frequency at which the image is refreshed (updated in the image it shows/displays), usually expressed in hertz, and can vary based on the content displayed on the screen.

LTTPR support is quickly becoming a cornerstone of next-gen DisplayPort architectures, particularly in automotive, industrial, and multi-display environments. Here's what you need to know.

This article breaks down the latest DisplayPort trends, the key technological shifts driving the protocol forward, and the strategic challenges implementers need to navigate — especially as DisplayPort IP finds its way into increasingly safety-critical domains.

DisplayPort uses Secondary Data Packets (SDPs), which are transported over the Main-Link that are not main video stream data. This allows it to carry audio and video simultaneously. The VIP supports audio transmission both in the original mode as defined in the specification as well as just as any other SDP being transmitted.

Cadence