DisplayPort Transmitter IP

Our 6th generation DisplayPort Transmitter Link Controller core supports DisplayPort 2.1, DisplayPort 1.4a and embedded DisplayPo…

Overview

Our 6th generation DisplayPort Transmitter Link Controller core supports DisplayPort 2.1, DisplayPort 1.4a and embedded DisplayPort 1.5.

Features include link rates up to 20Gbps for DisplayPort 2.0, 8.1Gbps for DisplayPort 1.4a. Display Steam Compression (DSC), multi-stream transport (MST) and more. The base core includes all required link functionality— Main Link, Secondary Channel, and AUX Channel protocols—and supports the HDCP 2.3 standards for data encryption.

The DisplayPort Transmitter core interfaces use common industry standards for low-complexity integration.

Video In

Streaming interface with industry-standard flow control, including separate syncs and data enable. Frame and line delimiter signals are supported with either 1, 2 or 4 pixels per input clock cycle.

42-bit pixel inputs provide deep color support. Other color depths are chosen through selective use of these input ports.

Audio

Multi-port I2S interface with up to 32 audio channels for digital audio transport.

Host

32-bit AMBA Peripheral Bus (APB), 4 slave port for low-complexity transfers of configuration information to the core.

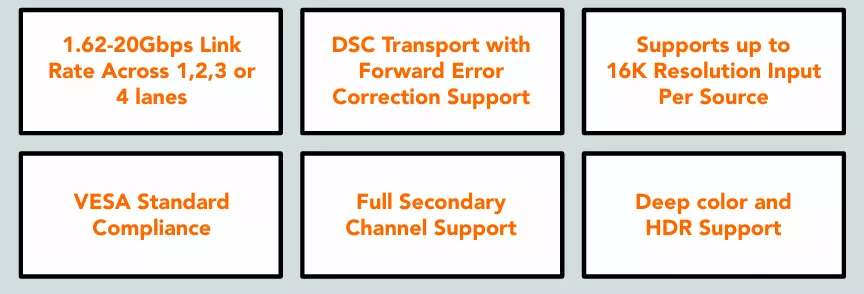

Key features

- Silicon proven on multiple ASIC and FPGA processes with multiple PHY partners

- 1, 2 or 4 pixels per input cycle, supporting up to 16K resolution input per source

- 1.62-20Gbps (8.1Gbps max for 1.4a) link rate across 1, 2, 3, or 4 lanes

- SST or MST operation

- Full secondary channel support

- Real time HDCP 1.4/2.3 support

- Optional eDP 1.5 support including enhanced Panel Replay Protocol

- Meets VESA Standard Compliance

- Deep color and HDR support up to 16 bits of color

- DSC transport with Forward Error Correction support

- Interfaces to external PHY. Compatible with 3rd-party PHYs for ASICs from 7nm to 65nm technologies; FPGA-targeted implementations are also available

Block Diagram

What’s Included?

- HDL source files for the function design

- Fully functional models for block-level and top-level testing, including over 120+ tests in the user level environment

- Functional specification

- Timing constraints summary document

- IP-XACT register descriptions

- Generic SRAM simulation models

- C Reference Driver

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Displayport IP core

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

DisplayPort 2025: Navigating the Next Wave of Display Innovation

Audio Transport in DisplayPort VIP

DisplayPort 2.1 vs DisplayPort 1.4: A Detailed Comparison of Key Features

Frequently asked questions about DisplayPort IP cores

What is DisplayPort Transmitter IP?

DisplayPort Transmitter IP is a Displayport IP core from Trilinear Technologies, Inc. listed on Semi IP Hub.

How should engineers evaluate this Displayport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Displayport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.