DVB-RCS2 Multi-Carrier Receiver

DVB-RCS2 (Digital Video Broadcast – Second Generation DVB Interactive Satellite System) is the latest ETSI standard of the second…

Overview

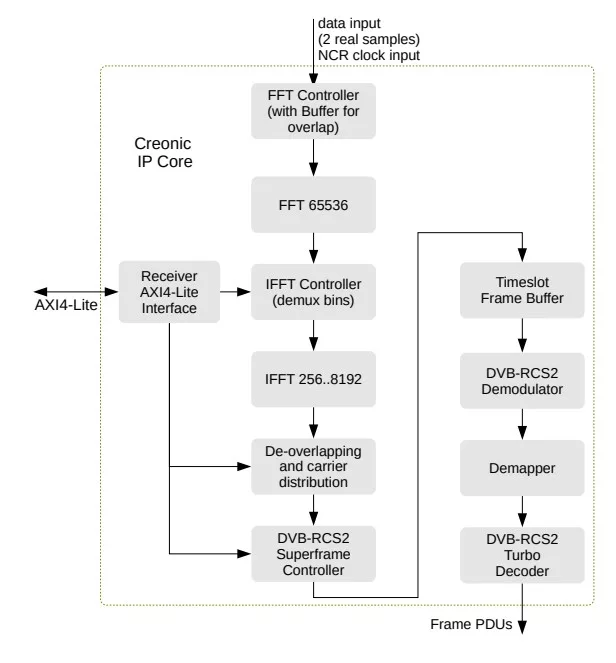

DVB-RCS2 (Digital Video Broadcast – Second Generation DVB Interactive Satellite System) is the latest ETSI standard of the second generation for digital data transmission via satellites.The Creonic DVB-RCS2 Multi-Carrier Receiver IP core supports multiple frequency time domain multiple access (MF-TDMA), performs all tasks of an DVB-RCS2 receiver including carriers separation, baseband conversion, demodulation, and turbo decoding. It can process intermediate frequency (IF) real signal with center IF frequencies between 0 and 100 MHz.

The turbo decoder is included in the receiver to provide users with Frame PDUs at the output.

Key features

- Compliant with ETSI EN 301 545-2 (DVB-RCS2)

- Support for Linear Modulation Bursts of Table A-1

- Optional support for Spread-spectrum Linear Modulation Burst waveforms of Table A-2

- Support for BPSK, QPSK, 8-PSK, 16-QAM

- Supports real, intermediate frequency signal at input

- Supports 32 carriers at aggregate symbol rate of 50 MSymbols/s, sample rate of 200 MSamples/s

- Supports symbol rate per carrier from 200 kSymbols/s to 12.5 MSymbols/s at an input rate of 200 MSamples/s

Block Diagram

Benefits

- Supports MF-TDMA using the DVB-RCS2 protocol

- The receiver performs multi-carrier processing, including gain adjustment, timing correction, decimation, filtering, bursts synchronization, derotation, decrambling, phase and frequency correction, DVB-RCS2 deframing, turbo decoding, and CRC-16 / CRC-32 checks

- On-the-fly reconfiguration of superframe and number of active carriers

- Configurable amount of turbo decoder iterations

- Low-power and low-complexity design.

- AXI4-Lite interface for controlling and for retrieving status information

- Collection of statistics (error rates, superframe and timeslot counters, frequency and timing offsets, signal-to-noise ratio (SNR))

- Validated on Xilinx RFSoC board with the Creonic DVB-RCS2 modulator

- Available for ASIC and FPGAs (AMD Xilinx, Intel)

Applications

- Satellite communication (Digital Video Broadcasting, Interactive Services, Professional Services, News Gathering)

What’s Included?

VHDL source code or synthesized netlist

HDL simulation models e.g. for Aldec’s Riviera-PRO

VHDL testbench

bit-accurate Matlab, C or C++ simulation model

Comprehensive documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is DVB-RCS2 Multi-Carrier Receiver?

DVB-RCS2 Multi-Carrier Receiver is a Channel Coding IP core from Creonic listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.