DVB-Satellite FEC Decoder

The CMS0077 Satellite FEC Decoder has been designed specifically to meet the requirements of the DVB-S2 and DVB-S2X wide-band dig…

Overview

The CMS0077 Satellite FEC Decoder has been designed specifically to meet the requirements of the DVB-S2 and DVB-S2X advanced wide-band digital satellite standards.

The core provides all the necessary processing steps to convert a demodulated complex I/Q signal into a standard TS output stream.

If configured for ACM operation, the FEC mode can dynamically change on a frame-by-frame basis. The design has been optimised to provide excellent performance in FPGA devices.

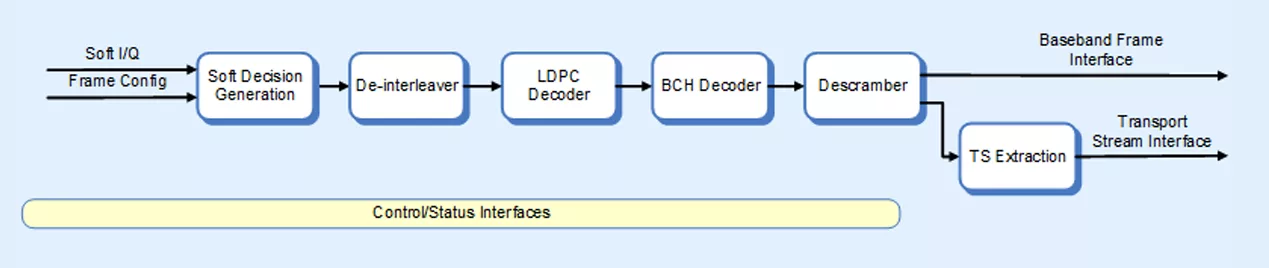

A description of the processing steps follows:

- Soft Decision Generator. This block calculates the Log Likelihood Ratios (LLRs) for individual bits encoded in the complex IQ symbols received from the demodulator.

- De-Interleaver. Reverses the block-interleave and writes LLR data into the LDPC input buffer. LDPC Decoder. Performs LDPC decoding of both the main payload data and also the TMCC Header. The decoder uses a modified min-sum algorithm for optimum performance end efficient resource usage. BCH Decoder. Error-checks the LDPC output and corrects small numbers of residual LDPC errors. Provides reliable detection of uncorrectable decoding errors which are then flagged in the output stream. De-Scrambling. Reverses the energy dispersal randomisation using the DVB-S2 scrambling polynomial.

- TS Rate Adaption. The Decoder output can be optionally configured to produce a constant-rate TS whose byte-rate tracks the off-air symbol rate. Register Bank. The register bank provides a simple 32-bit interface for reading status registers within the decoder block. Full details of the registers are contained in the IP Users Guide.

Key features

- Fully compliant with ETSI EN-302307-1 / -2.

- The IP core accepts demodulated digital IQ inputs and is designed to interface directly with the CMS0059 DVB-S2 / DVB-S2X Demodulator core.

- Supports QPSK, 8-PSK, 16/32/64/128/256-APSK modes.

- Includes Soft-Decision Slicing, De-Interleaving, LDPC Decoding, De-Scrambling and BCH Decoding.

- Configurable output can support either raw Base Band Framing data or can generate a constant-rate TS output.

- Synthesis options to tailor resource usage to required performance.

- Designed for very efficient FPGA implementation without compromise to the targeting of gate array or standard cell structures.

- Supplied as a protected bitstream or netlist (Megacore for Altera FPGA targets

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Our expertise is primarily in the gate- and power-efficient implementation of physical-layer (PHY) functions such as: modulation, demodulation, equalisation and channel coding but our experience encompasses all of the major elements of a modern baseband 'core' including the medium access control (MAC), voiceband DSP, mixed-signal interfaces, and embedded Cpu and software.

Our services are provided on a turnkey basis or as part of a support package attached to our licenced IP or tool products.

Commsonic's customers are typically semiconductor vendors and manufacturers of communications equipment that require leading-edge, Standards-based or proprietary PHY solutions but lack the internal resources or skills necessary to deliver projects against aggressive deadlines.

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is DVB-Satellite FEC Decoder?

DVB-Satellite FEC Decoder is a Channel Coding IP core from Commsonic Ltd listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.