Double & Single Precision IEEE-754 complete FPU

The A2FD is a fully synthesizable module implemented in Verilog RTL.

Overview

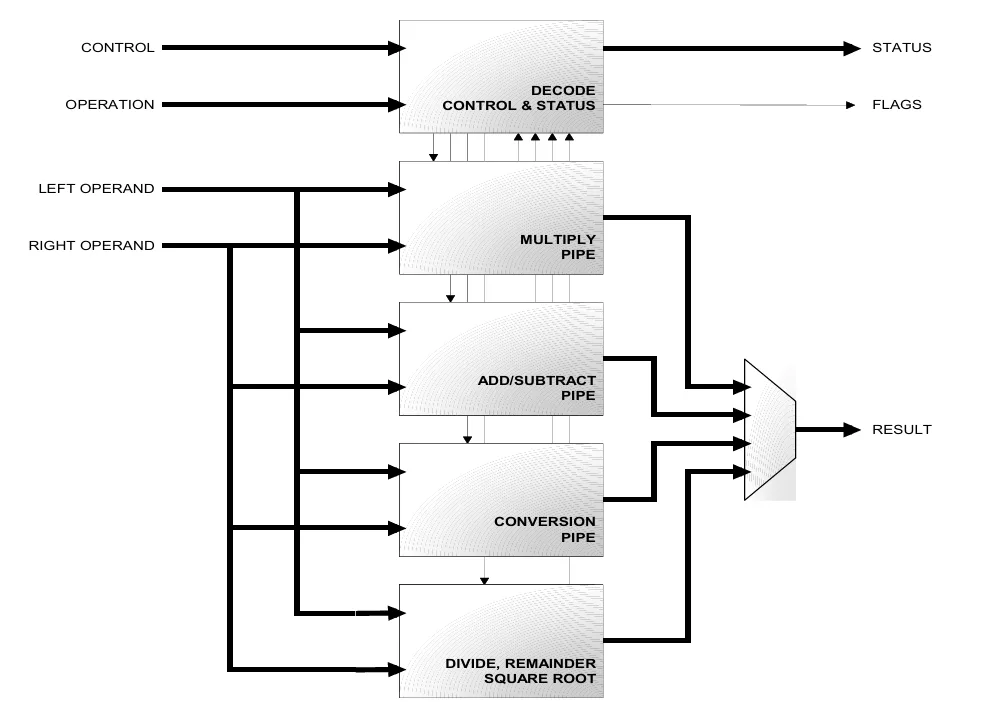

The A2FD is a fully synthesizable module implemented in Verilog RTL. It is a co-processor unit providing floating-point computation compliant with the ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-Point Arithmetic (IEEE Standard). It is designed to provide high performance floating-point computation while minimizing die size and power. Pipelined, single-cycle throughput operation is available for all operations except Divide, Remainder and Square Root operations.

The Multiply and Add/Subtract Pipes maybe optionally be replaced with a full Fused Multiply-Add Pipe that provides improved precision for complex operations.

The A2FD implements most of the formats and operations specified in the IEEE 754 standard directly in its hardware pipelines. The following operations are not supported directly by the A2FD, but can be supported with software support:

- Denormal numbers

- Underflow to denormal numbers

- Full NaN support

- BCD conversions

Control Register bits determine how the A2FD treats denormals and NaN operands, and underflow conditions. In Fast Mode, input denormal operands are treated as equivalent to positive zero. When an arithmetic operation generates an underflow result, the A2FD returns a zero instead (flush-to-zero mode). When an arithmetic instruction generates a NaN operand, the default NaN value is always generated. The A2FD does not propagate the lower mantissa bits of NaNs. In Compliance Mode, the A2FD will generate a software trap when it encounters a denormal input, generates an underflow value, or needs to generate a NaN result. This allows support software to complete the trapped operation in a way that is fully compliant with the IEEE standard.

Key features

- Fully Synthesizable RTL - Verilog

- User Selectable Precision

- Single precision

- Double precision

- IEEE 754 fast mode compliant

- Supports all IEEE rounding modes

- Extensible to run complex Math Functions

- Addition of sequencer and ROM allows trigonometry and other complex functions

- C models available

- Fully Synchronous pipelines

- Three stage pipeline

- Full enhanced IEEE 754 Compliance Suite

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about FPU IP core

A formal-based approach for efficient RISC-V processor verification

Efficient Verification of RISC-V processors

Formally Verifying Processor Security

JasperGold: the Next Generation

NXP Introduces Tensilica HiFi 4 DSP-based Platforms to Secure IoT Edge Devices

Frequently asked questions about FPU IP cores

What is Double & Single Precision IEEE-754 complete FPU?

Double & Single Precision IEEE-754 complete FPU is a FPU IP core from Advanced Architectures listed on Semi IP Hub.

How should engineers evaluate this FPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this FPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.