I2C Slave DO-254 IP Core

The I2C Slave IP Core implements an I2C Slave fully compliant to the I2C-bus specification and user manual Rev.

Overview

The I2C Slave IP Core implements an I2C Slave fully compliant to the I2C-bus specification and user manual Rev. 5 – 9 October 2012 for Standard-mode, Fast-mode and Fast-mode Plus (Fm+).

The Inter-Integrated Circuit (I2C) is a multi-master, multi-slave, single-ended, serial computer bus invented by Philips Semiconductor (now NXP Semiconductors). The I2C bus is typically used for attaching lower-speed peripheral ICs to processors and microcontrollers.

The I2C Master IP Core has been developed to DAL A according to the DO-254 / ED-80 and is accompanied by a Certification Kit. For lower DAL levels reduced documentation sets are available. The core is also available as a netlist for DAL D or projects not needing the full RTL source.

Safe Core Devices provides two separate IP Cores, one for the I2C Slave IP Core and one for the I2C Master IP Core. If the system needs to be capable of transmitting and receiving both cores can be instantiated in the target device.

Key features

- Design Assurance Level A according to RTCA DO-254/ED-80 (April, 2000)

- Fully compliant to the I2C-bus specification and user manual Rev. 5 – 9 October 2012 for Standard-mode, Fast-mode and Fast-mode Plus (Fm+)

- Configurable data rate (100kHz, 400kHz or 1000kHz)

- Support for all Options (Multi-master, Synchronization, Arbitration, Clock stretching, 10-bit slave address, General Call address, Software Reset and START byte)

- Single clock domain fully synchronous design

- Simple interface to user’s logic

- TMR coded for SEU immunity (optional)

- Technology independent (can be synthesized to any FPGA/CPLD vendor)

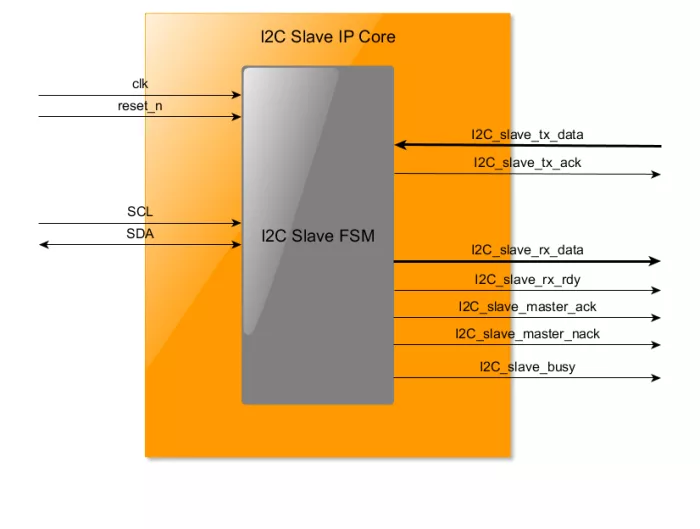

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about I2C / I3C IP core

Maximizing the Usability of Your Chip Development: Design with Flexibility for the Future

MIPI I3C v1.1 - A Conversation with Ken Foust

How to Connect Sensors with I3C

MIPI CCI over I3C: Faster Camera Control for SoC Architects

Arasan I3C PHY - Ternary vs. Non-Ternary

Frequently asked questions about I2C / I3C IP cores

What is I2C Slave DO-254 IP Core?

I2C Slave DO-254 IP Core is a I2C / I3C IP core from SafeCore Devices listed on Semi IP Hub.

How should engineers evaluate this I2C / I3C?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2C / I3C IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.