Die-to-Die PHY

The NuLink technology delivers low-power and high-performance D2D IP core products, which support multiple industry standards and…

Overview

The NuLink technology delivers low-power and high-performance D2D IP core products, which support multiple industry standards and are available on both standard and advanced packaging.

The vendor uses its NuLink technology to develop die-to-die PHY IP products to support multiple standards (including UCIe and BoW) and multiple packaging types (including advanced packaging and standard packaging).

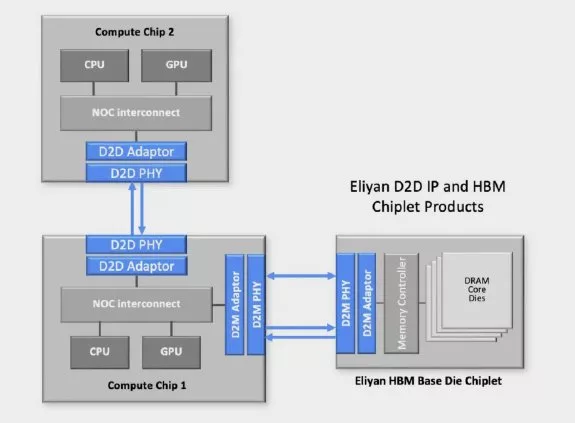

For Standard Packaging, the vendor has a family of high-bandwidth interface IP cores that are designed to be integrated into ASIC designs to connect two dies (chiplets) on the same standard organic/laminate package substrate. The PHY technologies with patented implementation techniques enable the same levels of performance and power as those provided by advanced packaging options, while providing benefits to system design, cost, thermal, test, yield, and production cycle-time by utilizing industry standard packaging. In many applications this eliminates the need for advanced packaging technologies such as silicon interposers or silicon bridges.

Block Diagram

Applications

- Chiplets connected on standard organic packages without large silicon interposers or silicon bridges but with interposer-like bandwidth/power/latency.

- SiP applications that benefit from up to at least four times the substrate area compared to the largest silicon interposer and thus a far higher number of chiplets in the package, resulting in major performance and power advantages.

- ASIC designs where a Network on Chip is split across two or more chiplets.

- Applications that benefit from placement flexibility to mix and match chiplets of different dimensions.

- Chiplet applications–such as HBM—where there must be physical separation between a hot ASIC and heat-sensitive dies.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Custom IP core

Breaking the Bandwidth Barrier: Enabling Celestial AI’s Photonic Fabric™ with Custom ESD IP on TSMC’s 5nm Platform

A New Era for Edge AI: Codasip’s Custom Vector Processor Drives the SYCLOPS Mission

RISC-V basics: The truth about custom extensions

Automatically Retargeting Hardware and Code Generation for RISC-V Custom Instructions

Unlock early software development for custom RISC-V designs with faster simulation

Frequently asked questions about Custom Die-to-Die IP cores

What is Die-to-Die PHY?

Die-to-Die PHY is a Custom IP core from Eliyan listed on Semi IP Hub.

How should engineers evaluate this Custom?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Custom IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.