Lattice Mico8 Open, Free Soft Microcontroller

The LatticeMico8 is an 8-bit microcontroller optimized and fully tested for the MachXO2™ family of Programmable Logic Devices (PL…

Overview

The LatticeMico8 is an 8-bit microcontroller optimized and fully tested for the MachXO2™ family of Programmable Logic Devices (PLDs). It can also be used as a reference design for the other families of Field Programmable Gate Arrays (FPGAs). Combining a full 18-bit wide instruction set with 32 general purpose registers, the LatticeMico8 is suitable for a wide variety of markets, including communications, consumer, computer, medical, industrial, and automotive. The core consumes minimal device resources, less than 200 Look Up Tables (LUTs) in the smallest configuration, while maintaining a broad feature set.

The LatticeMico8 is licensed under a new open intellectual property (IP) core license, the first such license offered by any FPGA supplier. The main benefits of using open source IP are greater flexibility, improved portability, and no cost. This new agreement provides all the benefits of standard open source and allows users to mix proprietary designs with the open source core. Additionally, it allows for the distribution of designs in bitstream or FPGA format without accompanying it with a copy of the license.

Development Tools

LatticeMico System is to be used to implement a LatticeMico8 micro-controller system with attached peripheral components. It is based on the Eclipse C/C++ Development Tools environment, which is an industry open-source development and application framework for building software.

Key features

- Innovative Open IP Core License

- Efficient Architecture and Broad Feature Set

- 18-bit Wide Instructions

- Configurable 16 or 32 General Purpose Registers

- Configurable Instruction Memory (PROM)

- Internal or external through Wishbone Interface

- Configurable to accomodate 256, 512, 1K, 2K or 4K instructions

- Scratchpad Memory

- Internal or external through Wishbone Interface

- Configurable up to 4 Gigabytes using paging (256 bytes per page)

- Mimimum two cycles per instruction

- Configurable 8, 16, or 32-deep call stack

- Support for up to 8 external interrupts

- Integrated hardware loader to optionally initialize PROM and Scratch pd for an external non-volatile mem

- Wishbone Peripheral Components:

- GPIO, UART, DMA Controller, SPI Flash Controller, MachXO2 EFB (I2C, SPI, Timer)

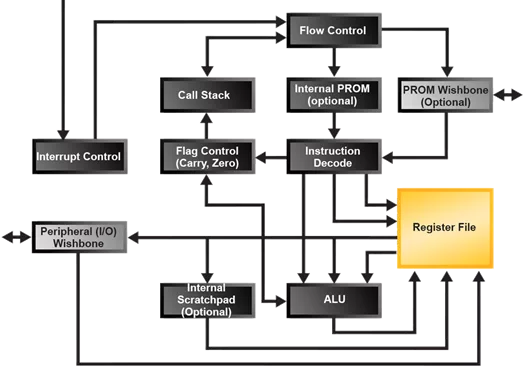

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MCU IP core

Why Did Ambiq Micro Select HiFi-5 DSP IP for Next Generation MCU?

Upgrading 8- and 16-bit MCU designs: Development ecosystem

Adding DSP hardware shrinks energy for MCU core

Advanced BLDC Motor Control using Freescale Ultra Reliable MPC5676R/MPC5674F MCU

Cortex-M7: 6-stage, cached, 400 MHz MCU

Frequently asked questions about MCU IP cores

What is Lattice Mico8 Open, Free Soft Microcontroller?

Lattice Mico8 Open, Free Soft Microcontroller is a MCU IP core from Lattice Semiconductor Corp. listed on Semi IP Hub.

How should engineers evaluate this MCU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MCU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.