Ku-Band Phased Array Rx-FE in TSMC 180nm RF

The TRV501TSM180RF IP is a Ku-Band (10.7GHz to 12.75GHz) Receiver (Rx) RFFE TSMC 180nm RF CMOS process technology.

Overview

The TRV501TSM180RF IP is a Ku-Band (10.7GHz to 12.75GHz) Receiver (Rx) RFFE TSMC 180nm RF CMOS process technology. It integrates X+Y receiver channels on the same die and its low noise figure and wide baseband bandwidth makes it especially suitable for use in high-throughput modular digital Phased-Array Antenna products for mobile/tethered satellite communication applications.

Key features

- 10.7GHz to 12.75GHz RF Input Bandwidth

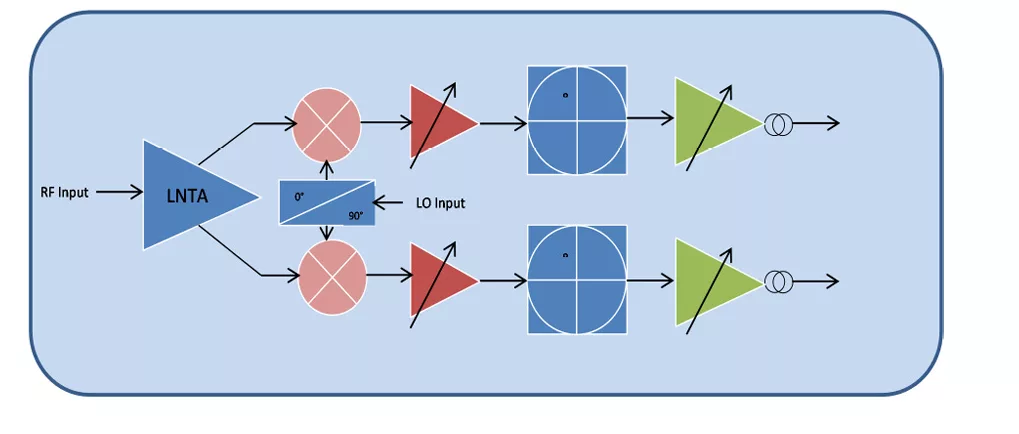

- Direct down-conversion and IQ Generator Circuitry

- Dual X + Y LNA

- -10dB S11

- 80mA Current Consumption

- 4dB Noise Figure

- -20dBm IIP3

Block Diagram

What’s Included?

- Behavioural Models

- Layout Abstract View

- Timing Models

- GDSII Layout Database

- Netlist for LVS verification

- Usage and Integration Guidelines

- Databook

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 180nm | RF | — |

Specifications

Identity

Provider

Learn more about RF Front End IP core

Micros benefit from ASIC heritage

Tools for Test and Debug : Specialized net backplanes needed for DSP debug in distributed environments

Software radio closes in on handsets

DSP/ASIC approach offers processing benefits for 802.11b implementation

Is there a "one-size fits all" SOC PLL?

Frequently asked questions about RF Front End IP cores

What is Ku-Band Phased Array Rx-FE in TSMC 180nm RF?

Ku-Band Phased Array Rx-FE in TSMC 180nm RF is a RF Front End IP core from Tetrivis listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this RF Front End?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this RF Front End IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.