800G Ethernet Verification IP

The 800GBase-KR16 Ethernet Verification IP is compliant with IEEE 802.3bs specifications and verifies MAC-to-PHY layer interfaces…

Overview

The 800GBase-KR16 Ethernet Verification IP is compliant with IEEE 802.3bs specifications and verifies MAC-to-PHY layer interfaces of designs with a 800GBase-KR16 Ethernet interface. It can work with SystemVerilog, Vera, SystemC, E and Verilog HDL environment. 800GBase-KR16 verification IP is developed by experts in Ethernet, who have developed ethernet products in companies like Intel, Cortina-Systems, Emulex, Cisco. We know what it takes to verify a ethernet product.

800G Ethernet Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

800G Ethernet Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports 800GBase-KR16 interface as per the specification defined in IEEE 802.3bs

- Supports 800GMII

- Supports scrambler

- Supports FEC

- Supports backplane auto-negotation

- Supports Upper layer protocols.

- Supports IP in IP

- Supports Q in Q

- Supports CDR for serial protocols

- Supports MDIO slave and master model as per Clause 22 and Clause 45

- Supports Pause frame generation and detection.

- Supports Glitch insertion and detection

- Supports all types of 800GBase-KR16 TX and RX errors insertion/detection.

- Oversize, undersize, inrange, out of range Packet size errors

- Missing SPD/EPD/SFD framing errors

- SFD on wrong lane

- CRC Error

- Lane skew insertion

- Invalid /D/ and /K/ character injection

- Variable preamble and IPG insertion

- Invalid block code insertion

- Sync bit corruption

- FEC error injection

- Scrambler error injection

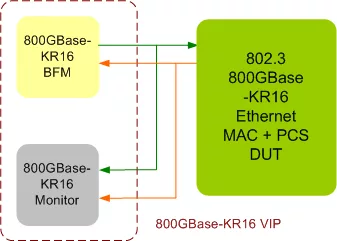

- Comes with 800GBase-KR16 Tx BFM, 800GBase-KR16 Rx BFM and 800GBase-KR16 PCS Monitor

- Monitor supports detection of all protocol violations.

- Built in coverage analysis.

- Callbacks in master and slave for various events

- Status counters for various events in bus

Block Diagram

Benefits

- Faster testbench development and more complete verification of 800GBase-KR16 designs.

- Easy to use command interface simplifies testbench control and configuration of 800GBase-KR16 TX and RX.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the testcases.

- Examples showing how to connect various components and usage of TXRX BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is 800G Ethernet Verification IP?

800G Ethernet Verification IP is a Ethernet IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.