High Speed Single Port Compiler on TSMC 40nm ULP

Single port SRAM compiler with low power retention mode Bit Cell Power Supply (V) 6T 1.1 Process Technology TSMC 40nm ULP Supply …

Overview

Single port SRAM compiler with low power retention mode

| Bit Cell | Power Supply (V) |

| 6T | 1.1 |

| Process Technology | TSMC 40nm ULP |

| Supply Voltage | 0.72V to 1.21V |

| Operating Temperature | -40°C to +125°C |

| Operating Frequency | 200MHz to 500MHz |

| # Metal Layers | 4 |

| Power | Mesh |

| BIST Mux Interface | Internal |

| Operational Modes | Functional, BIST and Scan |

| Max Instance | 512Kb |

| Min Instance | 256b |

| Word Width | 4–128 |

| Word Depth | 64–8192 |

| Aspect Ratio | Column Fold, 8 or 16 |

| Bit Write Enable | Optional |

| User Interface | GUI & Command Line |

Key features

- Low voltage. Mobile Semiconductor's SP-HSLV-TS40ULPF memory compiler generates single-port SRAM instances using the TSMC 40nm ULP CMOS process. Each low voltage memory instance uses standard VT to optimize performance with high VT and source biasing to minimize standby currents. Read and write assist circuits ensure reliable operation with a power supply as low as 0.72V.

- Ultra low power data retention. Memory instances generated by the SP-HSLV TS40ULPF go into a deep sleep mode that retains data at minimal power consumption.

- Self biasing. The SP-HSLV-TS40ULPF’s internal self-biasing capabilities provide ease of IP integration.

- Soft error immunity. Robust, low voltage latches are used throughout designs.

- High yield. To ensure high manufacturing yield, the SP-HSLV-TS40ULPF utilizes TSMC’s high VT 6T (0.242µ2) bit cells and is consistent with TSMC’s Design for Manufacturing (DFM) guidelines for the 40nm ULP process.

- High usability. All signal and power pins are available on metal 4 while maintaining routing porosity in metal 4.

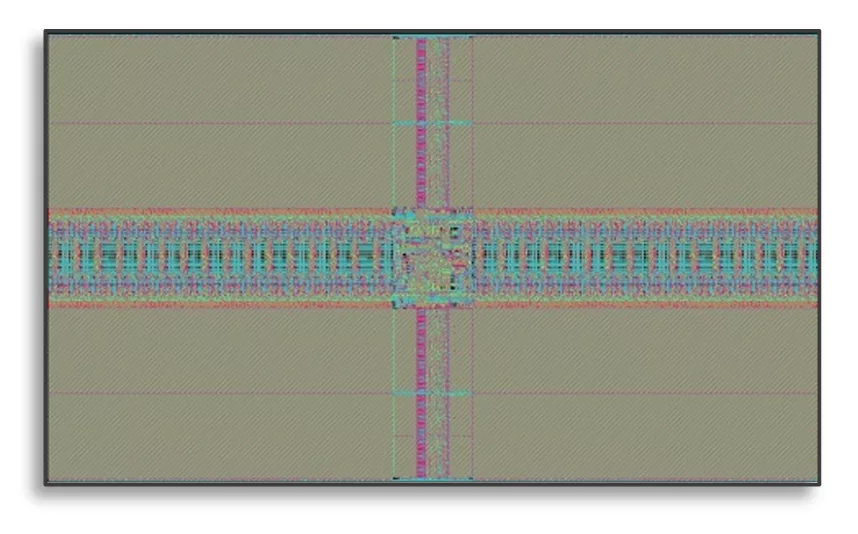

Block Diagram

What’s Included?

- GDS II Layout

- LVS SPICE Netlist

- Liberty File (NLDM and CCS)

- Verilog Model

- Verilog Netlist

- Verilog RTL Wrapper

- Verilog Test Bench

- ATPG Verilog

- LEF

- BIST Synthesis

- Control File

- Signal Integrity

- Analysis Models

- PDF and Text

- Datasheets

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 40nm | ULP eFlash | Silicon Proven |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about SRAM IP core

Novel Trade-offs in 5 nm FinFET SRAM Arrays at Extremely Low Temperatures

Why SRAM PUF Technology Is the Bedrock of Dependable Security in Any Chip

AI-driven SRAM demand needs integrated repair and security

A comparison of SRAM vs quantum-derived semiconductor PUFs

Basics of SRAM PUF and how to deploy it for IoT security

Frequently asked questions about SRAM IP cores

What is High Speed Single Port Compiler on TSMC 40nm ULP?

High Speed Single Port Compiler on TSMC 40nm ULP is a SRAM IP core from Nordic Semiconductor Seattle listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this SRAM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SRAM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.