ApSRAM Controller

The ApSRAM controller is a flexible, low-power, and low-latency solution designed for SRAM replacement in high-performance system…

Overview

The ApSRAM controller is a flexible, low-power, and low-latency solution designed for SRAM replacement in high-performance systems. Scalable from 64Mb to 1Gb, its multi-bank architecture enhances timing throughput, making it ideal for wearables, IoT devices, displays, automotive systems, industrial automation, and consumer electronics. Optimized for AI/ML, edge computing, and high-performance embedded systems, it supports seamless integration through its configurable AXI interface and adaptability across FPGA, Gate array, and Standard cell technologies. As part of Mobiveil’s Storage and Memory IP family, ApSRAM reflects expertise in creating system-validated, low-risk IP solutions for compliance and interoperability.

Key features

- Compliant with AXI4 and AP Memory specifications

- Configurable address width, queue depth, and FIFO size

- Supports self-refresh, auto-refresh, and power-down modes

- Intelligent request scheduling for optimized performance

- Maximizes bus efficiency with bank-level parallelism

- Built-in support for asynchronous DRAM frequencies

- Separate write and read queues with QoS control options

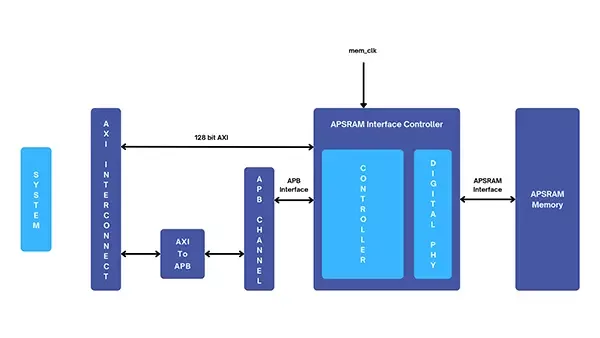

Block Diagram

Benefits

Specifications

- Built-in asynchronous interface support for DRAM frequencies that are not equal to the AXI frequency

- High, medium, normal, port priority

- Separate write and read queues

- The AXI ID signals support out-of-order transactions

Design Attributes

- Highly modular and configurable design

- Layered architecture

- Fully synchronous design

- Supports both sync and async reset

- Clearly demarked clock domains

- Software control for key features

What’s Included?

Product Package

- Configurable RTL Code

- HDL-based test bench and behavioral models

- Test cases

- Protocol checkers, bus watchers, and performance monitors

- Configurable synthesis scripts

Documentation

- Design Guide

- Verification Guide

- Synthesis Guide

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about SRAM IP core

Novel Trade-offs in 5 nm FinFET SRAM Arrays at Extremely Low Temperatures

Why SRAM PUF Technology Is the Bedrock of Dependable Security in Any Chip

AI-driven SRAM demand needs integrated repair and security

A comparison of SRAM vs quantum-derived semiconductor PUFs

Basics of SRAM PUF and how to deploy it for IoT security

Frequently asked questions about SRAM IP cores

What is ApSRAM Controller?

ApSRAM Controller is a SRAM IP core from Mobiveil Inc. listed on Semi IP Hub.

How should engineers evaluate this SRAM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SRAM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.