AGILEX 7 R-Tile Gen5 NVMe Host IP

The LDS NVME HOST IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

Overview

The LDS NVME HOST IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

The LDS NVME HOST IP provides two interfaces :

- One CPU interface for long sequential recording or reading.

- One FIFO interface for I/O intensive data transfer.

The register file interface simplify the management of the IP for CPU interface or State Machine interface using Avalon bus:

- PCIe RP and EP register configuration is done automatically.

- NVMe register configuration is done automatically.

- Able to manage 8 Name Spaces.

- Able to manage until 16 IO Queue to able Multi-users.

- Each IO Queue is independent.

- Able to manage 512Bytes or 4096Bytes sector size.

- Able to run nearly all Admin command in parallel of IO Queue.

- Some IO command already pre-defined to ease use of the IP.

- Configurable IO Queue buffer size to fit user memory requirement: 32KB, 64KB, 128KB, 256KB, 512KB or 1024KB.

- Able to read all PCIe RP and EP registers.

- Able to stop current command.

- Able to manage low data rate in reading.

- Easy connection to embedded Root Port R-Tile PCIe IP through Avalon bus.

- FAT32 / EXFAT available as an option.

The source code format is available for ease of customization. The customization can be done by Logic Design Solutions and DO254 documentation is available on request.

This IP can be customized according to specific needs (application-specific requirement). Any other pre-designed functions can be integrated into the FPGA. FPGA density and I/O requirements can be defined according to customer specification.

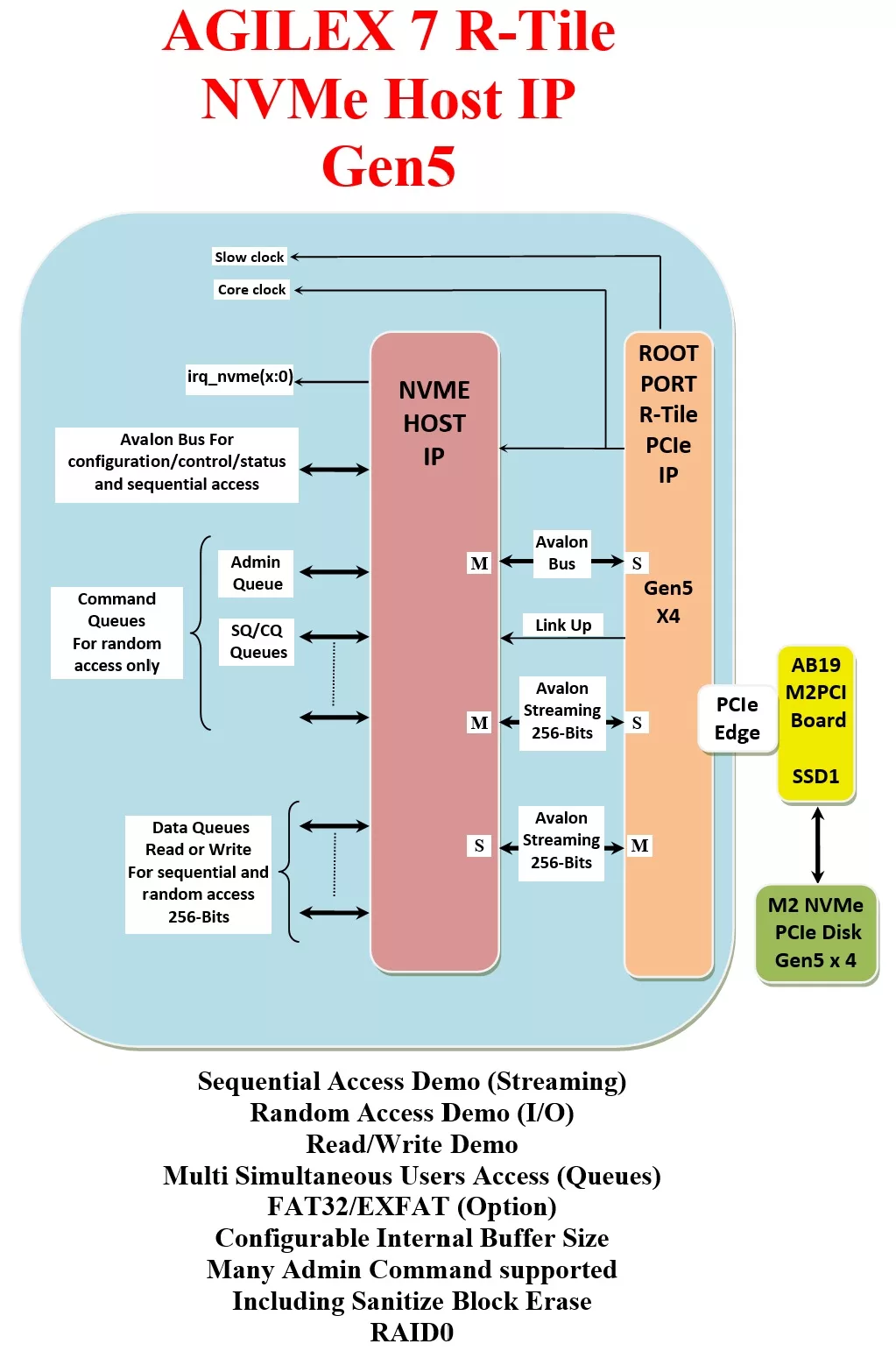

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about NVMe Controller IP core

NVMe powers SSDs in the enterprise

NVMe Emerges as Memory Independent

NVMe host IP for computing accelerator

NVMe IP for Enterprise SSD

Synopsys NVMe VIP Architecture: The Host Protocol Layers

Frequently asked questions about NVMe Controller IP cores

What is AGILEX 7 R-Tile Gen5 NVMe Host IP?

AGILEX 7 R-Tile Gen5 NVMe Host IP is a NVMe Controller IP core from Logic Design Solutions listed on Semi IP Hub.

How should engineers evaluate this NVMe Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this NVMe Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.