8-channel 8-bit voltage comparator

028TSMC_COMP_01 is a comparator that compares a reference voltage to an analog input voltage and contains 8 input channels with a…

Overview

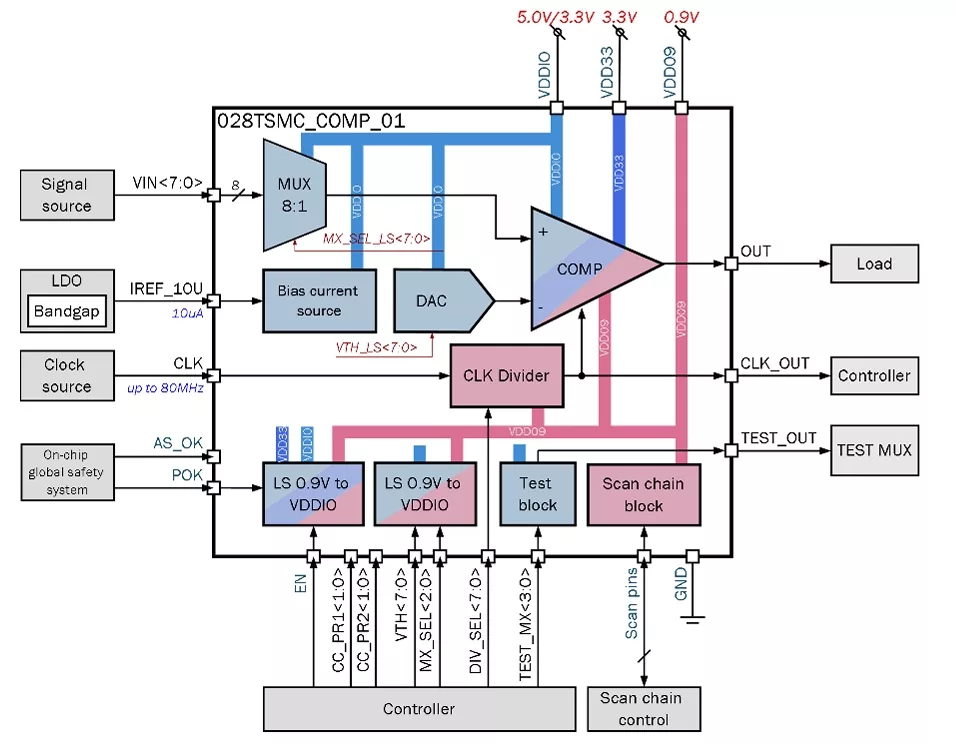

028TSMC_COMP_01 is a comparator that compares a reference voltage to an analog input voltage and contains 8 input channels with a programmable threshold, implemented using 8-bit digital-to-analog converter (DAC).

Conversion time is 25ns in worst case.

The block consists of input multiplexer 8:1, 8-bit DAC and 1-channel comparator.

The Comparator operates from analog VDDIO 3.3V/5.0V, VDD33 3.3V and digital voltage VDD09 0.9V. Bias currents should be delivered from an external source.

Key features

- TSMC 28nm eFlash technology

- 8 channel synchronous comparator

- 25ns conversion time

- Up to 80MHz external clock

- Current consumption in operation mode: 0.4mA@ VDDIO option 5.0V

- Analog IO supply voltage 5.0V (3.3V option)

- 3.3V supply voltage

- Core supply voltage 0.9V

- Automotive compliant: junction temperature: -40?C to +150?C

- Silicon area ~0.06mm2

Block Diagram

Applications

- Analog signal comparison

- Measurement environment

What’s Included?

- Schematic or NetList

- Abstract view (.lef and .lib files)

- Layout (optional)

- Verilog behavior model

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 28nm | 28nm 280 nm | Pre-Silicon |

Specifications

Identity

Provider

Learn more about Comparator IP core

Achieving Groundbreaking Performance with a Digital PLL

Improving Battery-Powered Device Operation Time Thanks To Power Efficient Sleep Mode

Generating High Speed CSI2 Video by an FPGA

Design & Verify Virtual Platform with reusable TLM 2.0

Metric Driven Verification of Reconfigurable Memory Controller IPs Using UVM Methodology for Improved Verification Effectiveness and Reusability

Frequently asked questions about Comparator IP cores

What is 8-channel 8-bit voltage comparator?

8-channel 8-bit voltage comparator is a Comparator IP core from NTLab listed on Semi IP Hub. It is listed with support for tsmc Pre-Silicon.

How should engineers evaluate this Comparator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Comparator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.