13ns High-Speed Comparator with no Hysteresis

The TS_CMP_13ns_X8 is a high-speed comparator with no hysteresis and a propagation delay of 13ns while having a differential inpu…

Overview

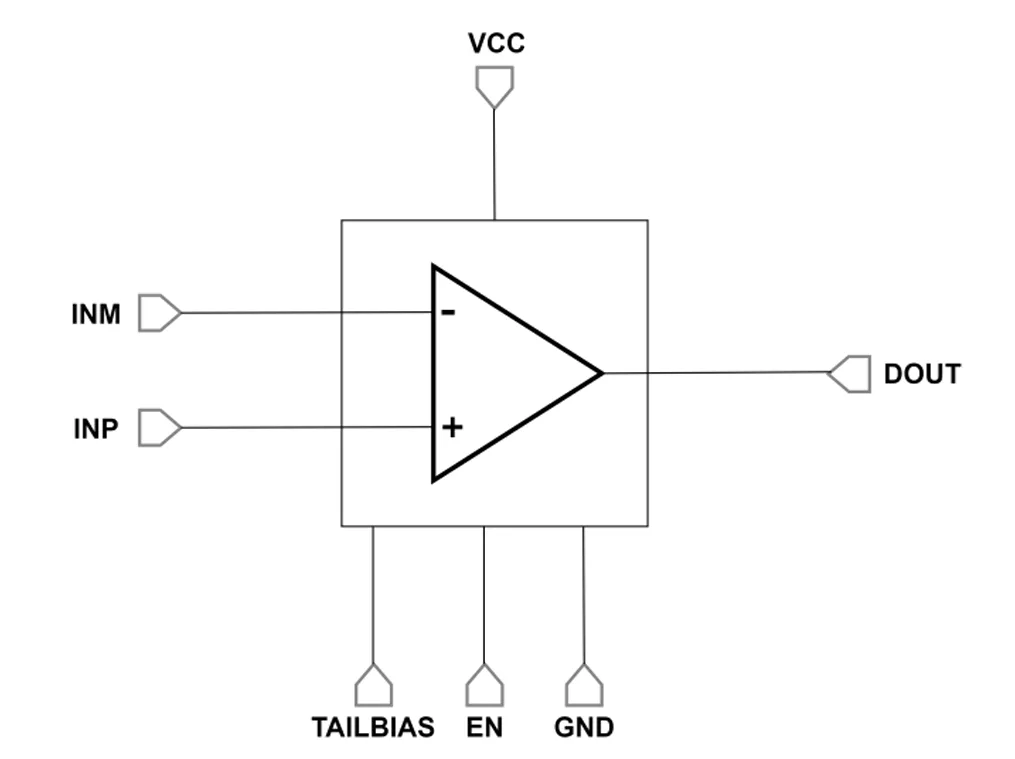

The TS_CMP_13ns_X8 is a high-speed comparator with no hysteresis and a propagation delay of 13ns while having a differential input signal of 25mV. The comparator consumes current of 350μA. The circuit features an Enable signal turning on/off the comparator. The proposed circuit is a free-running comparator, therefore, no clock signal is needed, as depicted in the comparator symbol in Figure 1. The comparator requires a bias current of 20uA supplied from an external biasing circuit and can provide an output toggling between 0V and Vcc. A comparator hysteresis can be added via feedback circuit.

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Comparator IP core

Achieving Groundbreaking Performance with a Digital PLL

Improving Battery-Powered Device Operation Time Thanks To Power Efficient Sleep Mode

Generating High Speed CSI2 Video by an FPGA

Design & Verify Virtual Platform with reusable TLM 2.0

Metric Driven Verification of Reconfigurable Memory Controller IPs Using UVM Methodology for Improved Verification Effectiveness and Reusability

Frequently asked questions about Comparator IP cores

What is 13ns High-Speed Comparator with no Hysteresis?

13ns High-Speed Comparator with no Hysteresis is a Comparator IP core from TES Electronic Solutions listed on Semi IP Hub.

How should engineers evaluate this Comparator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Comparator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.