Programmable-Threshold Comparator

The agileCMP GP Programmable Threshold Comparator features a user-selectable (enable/disable) hysteresis as well as programmable …

Overview

The agileCMP GP Programmable Threshold Comparator features a user-selectable (enable/disable) hysteresis as well as programmable threshold with 10mV step size, a latched output, as well as an active (unlatched) output. With a focus on long battery life, the agileCMP GP can be used to monitor external analog signals and enable wake-up events as is essential in many modern SoCs. The agileCMP GP Programmable Threshold Comparator is ideally suited for interrupt generation in applications such as in IoT, Security, Automotive, AI and general SoCs and ASICs.

Agile Analog designs are based on tried and tested architectures to ensure reliability and functionality. Our design methodology is programmatic, systematic and repeatable leading to analog IP that is more verifiable, more robust and more reliable. Our methodology also allows us to quickly re-target our IP to different process options. We support all the major foundries including TSMC, GlobalFoundries, Intel Foundry, Samsung Foundry, UMC and Other Foundries.

Key features

- Configurable to your specification

- Rail-to-rail input voltage range

- Low threshold offset voltage

- Programmable threshold voltage

- Programmable hysteresis

- Dynamic and static (latched) outputs

- Low propagation delay

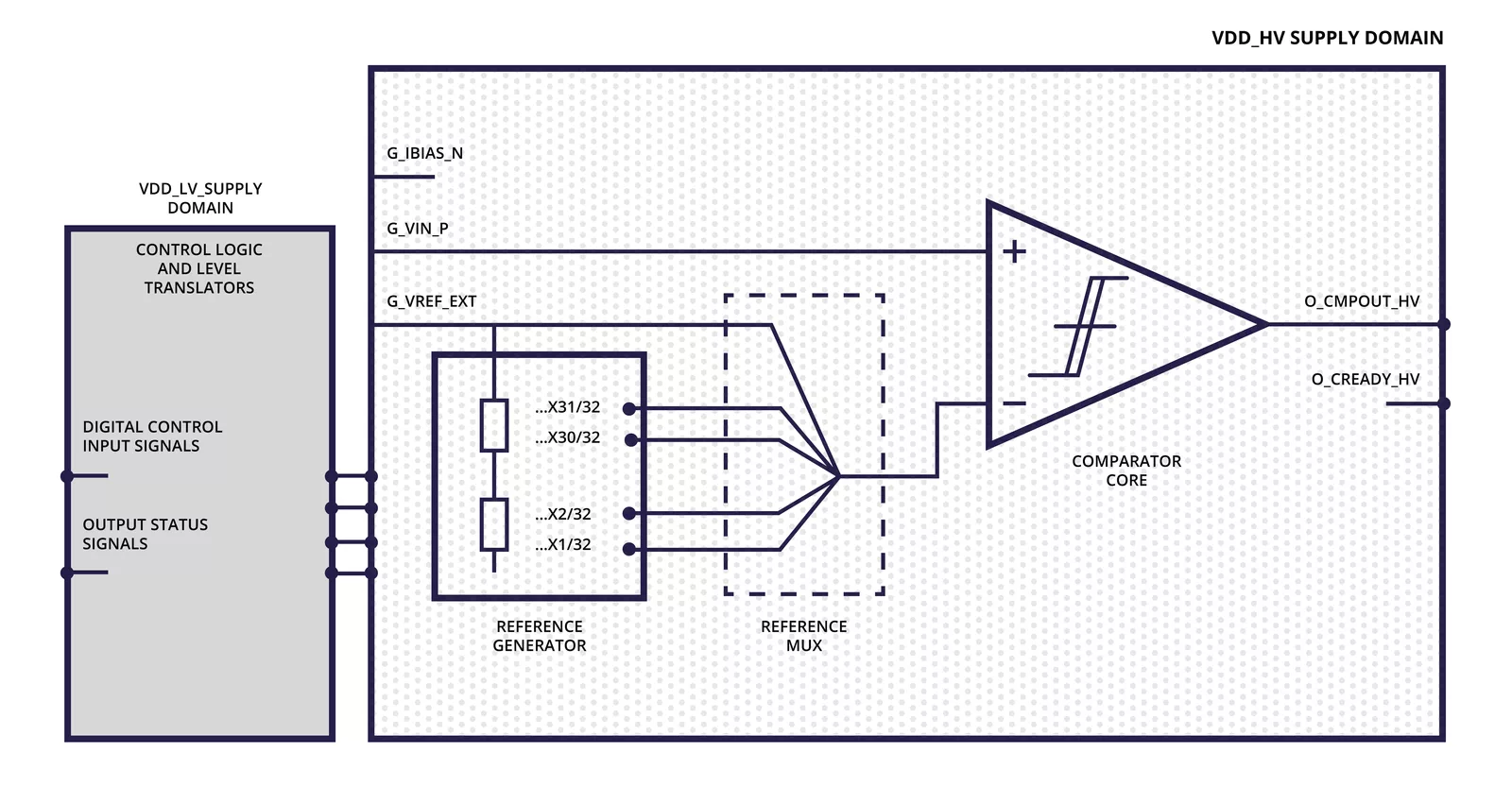

Block Diagram

Benefits

- Best-in-class deliverables for easy and seamless integration: our engineers have extensive experience taking complex SoCs from design to mass production

- We believe that success is not just measured by delivery of netlist and layout, rather it extends to mass-production and beyond

- Automated design procedure accelerates design time and enables quick re-centering with latest PDK updates so you can tape out with the latest foundry models

- Tried and tested architecture ensures reliability and functionality

Applications

- IoT, Security, Automotive, AI, SoCs, ASICs

What’s Included?

- Datasheet

- Testing and Integration Guide

- Verilog Models

- Floorplan (LEF)

- Timing models (LIB)

- Netlist (CDL)

- Layout (GDS)

- Physical Verification Report

- Design Report

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Comparator IP core

Achieving Groundbreaking Performance with a Digital PLL

Improving Battery-Powered Device Operation Time Thanks To Power Efficient Sleep Mode

Generating High Speed CSI2 Video by an FPGA

Design & Verify Virtual Platform with reusable TLM 2.0

Metric Driven Verification of Reconfigurable Memory Controller IPs Using UVM Methodology for Improved Verification Effectiveness and Reusability

Frequently asked questions about Comparator IP cores

What is Programmable-Threshold Comparator?

Programmable-Threshold Comparator is a Comparator IP core from Agile Analog listed on Semi IP Hub.

How should engineers evaluate this Comparator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Comparator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.