DOCSIS 3.1 LDPC Decoder (PLC / NCP / Data)

Data Over Cable Service Interface Specification (DOCSIS) is an international telecommunications standard that permits the additio…

Overview

Data Over Cable Service Interface Specification (DOCSIS) is an international telecommunications standard that permits the addition of high-bandwidth data transfer to an existing cable TV (CATV) system. It is employed by many cable television operators to provide Internet access over their existing hybrid fiber-coaxial infrastructure.

The DOCSIS 3.1 LDPC decoder IP cores are a complete solution for the downstream forward error correction, i.e. PLC decoder, NCP decoder and data decoder are included.

Key features

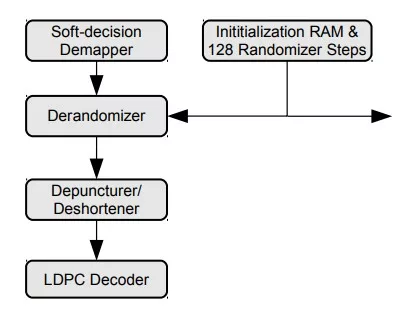

- Soft-Decision Demapper, Derandomizer, Deinterleaver, Depuncturer, and LDPC Decoder are included

- Support for 4k and 8K FFT sizes

- Support for 16-QAM modulation

- Features the NCP Decoder Core Supports

- Soft-Decision Demapper, Derandomizer, Deinterleaver, Depuncturer, Deshortener, and LDPC Decoder are included

- Support for 4k and 8K FFT sizes

- Support for QPSK, 16-QAM, and 64-QAM modulations

- Provides derandomization data for downstream data path

- Features the Data Decoder Core Supports

- Zero-bit Insertion, Parity Deinterleaver, LDPC Decoder, Shortener, and BCH Decoder are included

- Support for all block sizes, incl. shortening (3 to 1779 bytes)

- Data rate of more than 2.3 Gbit/s

Block Diagram

Benefits

- Low-power and low-complexity design.

- Frame-to-frame on-the-fly configuration.

- Faster convergence due to layered LDPC decoder architectures

- Early stopping criterion for iterative LDPC decoder, saving a considerable amount of energy

- Configurable amount of LDPC decoding iterations for trading-off throughput and error correction performance

- Collection of statistics (decoding success indicator, average number of iterations, modified bits)

- Available for ASIC and FPGAs (AMD Xilinx, Intel)

- Deliverable includes VHDL source code or synthesized netlist, VHDL testbench, and bit-accurate Matlab, C or C++ simulation model

Applications

- Cable TV networks

- Wired transmission with high demands on forward error correction

What’s Included?

- VHDL source code or synthesized netlist

- HDL simulation models e.g. for Aldec’s Riviera-PRO

- VHDL testbench

- Bit-accurate Matlab, C or C++ simulation model

- Comprehensive documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is DOCSIS 3.1 LDPC Decoder (PLC / NCP / Data)?

DOCSIS 3.1 LDPC Decoder (PLC / NCP / Data) is a Channel Coding IP core from Creonic listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.