1G TCP Offload Engine TOE +PCIe Very Low Latency (TOE+PCIe)

INT 1012 is the only SOC that integrates 1G TOE + 1 GEMAC + PCIe/DMA + Host interfaces in the smallest logic footprint.

Overview

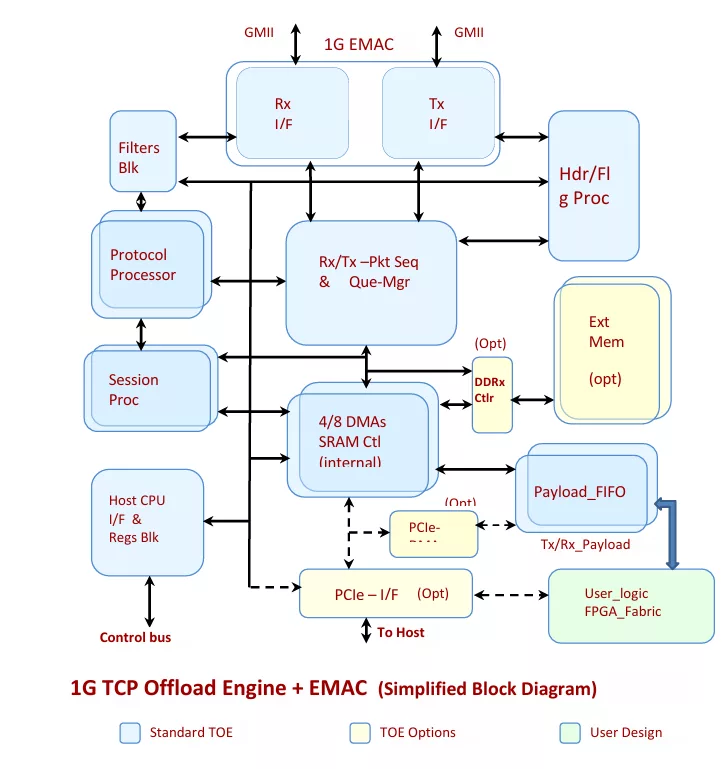

INT 1012 is the only SOC that integrates 1G TOE + 1 GEMAC + PCIe/DMA + Host interfaces in the smallest logic footprint. It is highly flexible that is customizable for layer-3, layer 4-7 network infrastructure and network security systems applications. It is recommended for use in, among others, high performance Servers, NICs, SAN/NAS and data center equipment design applications. It provides key IP building blocks for very high performance 10-Giga bit Ethernet ASIC/ASSP/FPGAs.

INT 1012 has built in advanced architectural flexibility that provides capability for enterprises to differentiate their Network security and Network infrastructure appliances from others and customize them for their specific design application.

INT 1012 can process TCP/IP sessions as client/server in mixed session mode for Network equipment and in-line network security appliances, simultaneously, at 1-G-bit rate. This relieves the host CPU from costly TCP/IP software related session setup/tear down, data copying and maintenance tasks thereby delivering 8x to 15x TCP/IP network performance improvement when compared with TCP/IP software.

Intilop offers a wide range of TOE processing hardware cores for 10-GE to 1-GE applications using PCI Express or embedded system interfaces. TOE products support full TCP offload as well as conventional NIC mode operation (as an option in TCP Bypass Mode) and feature advanced PCIe/DMA software support (optional) where applications need little modification/integration to take advantage of TOE acceleration.

As an option, it provides easy-to-use frameworks for utilizing the Xilinx Virtex-5/6, Altera Stratix-IV/V and PCIe/DMA hardcore enabling rapid and efficient system application development. The 1 G Bit TOE is based upon the proven and mature patent pending 1 G bit TOE architecture from Intilop corporation.

The same architecture is scalable to 10G and 40G bit.

Key features

- Complete TCP offload engine. Full hardware implementation of Control plane and Data plane. Truely customizable

Block Diagram

Benefits

- Accelerates TCP/IP performance by 10-20 times

What’s Included?

- Netlist

- Source

- Verilog

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is 1G TCP Offload Engine TOE +PCIe Very Low Latency (TOE+PCIe)?

1G TCP Offload Engine TOE +PCIe Very Low Latency (TOE+PCIe) is a Ethernet IP core from Intilop Corp. listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.