1.6T Ethernet MAC IP

The 1.6T Ethernet MAC IP implements the functions required by the IEEE 802.3-2018 specification to communicate over Ethernet prov…

Overview

The 1.6T Ethernet MAC IP implements the functions required by the IEEE 802.3-2018 specification to communicate over Ethernet providing a simple frame-based interface to the system and a standardized interface to the PCS (Physical Control Block).

The IP is split into four 400Gbps channels which can be configured via software-controllable registers to operate together to support higher data rates. The MAC supports the following data-rates:

400 Gbps with up to four independent ports active simultaneously

800 Gbps with up to two 800 Gbps ports or one 800 Gbps and two 400Gbps ports active simultaneously

1600 Gbps as a single port

The application interface is a FIFO-based interface with four channels capable of transferring up to 4x512-bits of frame data per clock cycle and per direction. The PCS interface consists of four channels 320-bit wide each, encoded according to IEEE 802.3 Clause 117 (400GMII) and clock-synchronous to the corresponding PCS interfaces. The rate is controlled via per-channel PCS-driven data-enable signals for both transmit and receive directions.

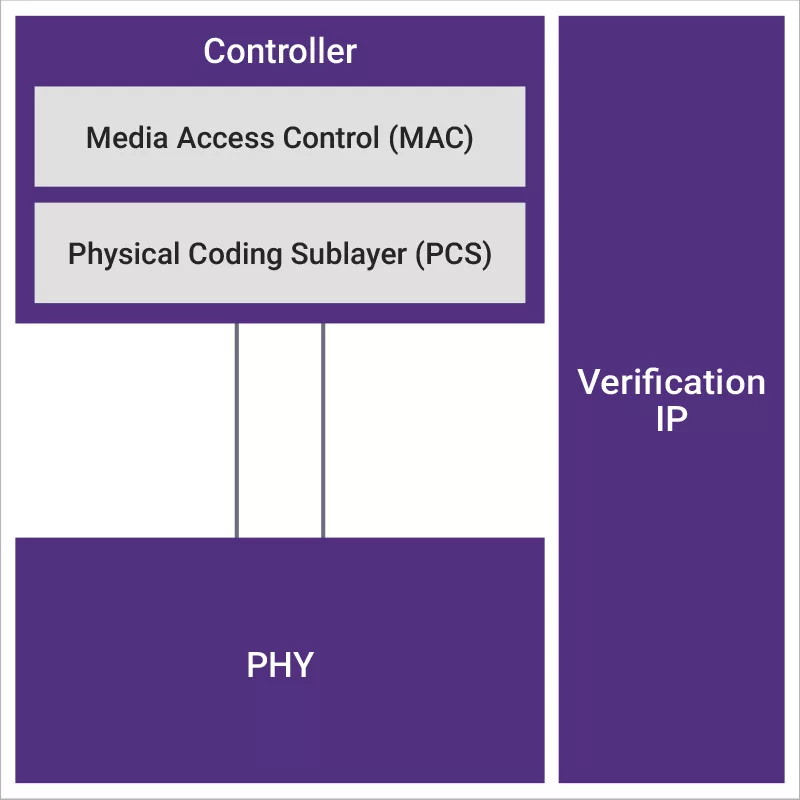

The 1.6T Ethernet MAC IP seamlessly interoperates with the 1.6T Ethernet PCS IP and the 224G Ethernet PHY IP to provide a complete Ethernet MAC, PCS and PHY solution for 1.6T systems.

Key features

- Supports all required features of the IEEE 802.3 specification

- Supports IEEE-managed objects, IETF MIB-II and RMON for management applications

- Application interface includes the Synopsys native interface 512-bit or 1024bit FIFO for more than 200G operation

- Integration tested with Synopsys 1.6T Ethernet PCS IP and 224G Ethernet PHY IP

- Supports IEEE 1588 applications

Block Diagram

Benefits

- Full MAC layer and reconciliation sublayer implementation compliant with the IEEE 802.3 specification.

- Up to four individual ports supporting full-duplex operation at 400Gbps, 800Gbps and 1600Gbps, with a maximum combined data-rate of 1600Gbps.

- IEEE 802.3 Clause 117 compliant 400GMII PCS interface with optional PCS-driven data-rate control.

- FIFO-based transmit application interface with simple level-based backpressure or accurate credit-based utilization.

- FIFO-based receive application interface with system backpressure support for fatal events resulting in immediate discard of received frames without compromising the interface.

- Protocol errors-resistant transmit application interface providing graceful recovery if a system error results in errors that compromise frame delimitation or causing the transmit buffer to overflow.

- Support for optional ECC or parity errors indication in both transmit and receive buffers (memories) that results in frame erroring.

- Fault detection and response as specified in Clause 81 of IEEE 802.3, supporting Local Faults, Remote Faults and Link Interrupt ordered set decoding and generation.

- Provision for Clause 78 of IEEE 802.3 (Energy Efficient Ethernet, amendment IEEE 802.3az) support and Low Power Idle (LPI) generation and detection.

- Transmit and receive per-frame statistics compliant with IEEE 802.3 and RFC 2819 and RFC 3635.

- Per-frame transmit and receive timestamp capture.

- Preamble, SFD and other framing characters insertion for transmitted frames, and check and removal deletion for received frames.

- IPG (Inter-Packet Gap) adjustment for rate compensation when using MACSEC engines.

- Frame FCS field checking and optional removal for received frames using CRC-32.

- Padding insertion for frames that are less than 64-bytes as transmitted from the application interface to the Synopsys 1.6T MAC IP.

- Optional Link Pause (IEEE 802.3 Annex 31B) and Priority Flow Control (IEEE 802.3 Annex 31D) frame generation and decoding with internal timers and programmable “Xoff” time duration.

- Optional support for frame modifications to support 1-step operation as defined in IEEE 802.3AS and IEEE 1588.

- Optional asynchronous system interface for easy decoupling of the MAC+PCS clock domain to the application clock-domain.

- Optional application-generated frame preamble and SFD for transmitted frames, and forwarding of frame’s preamble and SFD to the application for received frames.

- Generic host interface allowing direct access to all configuration and status registers.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is 1.6T Ethernet MAC IP?

1.6T Ethernet MAC IP is a Ethernet IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.