兆松科技 ZCC 工具链全面支持 Andes晶心科技 RISC-V 处理器

2023年7月31日 -- 芯片软硬件协同设计解决方案服务提供商兆松科技(Terapines Technology),宣布兆松科技的 ZCC 工具链全面支持晶心科技(Andes Technology; TWSE: 6533)全系列的 RISC-V 处理器。ZCC工具链目前在嵌入式、高性能、AI芯片等多个领域的表现都处于国际领先水平。Andes晶心科技是32及64位高效能、低功耗RISC-V处理器核心领导供货商、RISC-V国际协会(RISC-V International) 的创始首席会员,也是将RISC-V推向主流的主导力量。近日,兆松科技也正式加入RISC-V International,成为其战略会员。ZCC全面支持AndeStar™ V5指令集,意味着晶心科技及其合作伙伴可以在V5架构的 RISC-V CPU产品中使用ZCC工具链以达到更高代码密度和性能,从而满足更加广泛的应用需求。

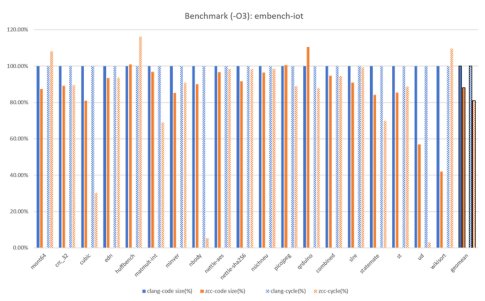

ZCC工具链相较晶心科技AndeSight™ IDE 所提供的LLVM编译器,可以进一步将AndesCore™ AX45 双发射8级流水线处理器CoreMark分数提升6%,在Embench-IoT(-O3)测试中同时实现了18.9%的性能提升和11.8%的代码密度优化;在Embench-IoT(-Os)测试同时实现了10%的代码密度优化和9.1%的性能提升。

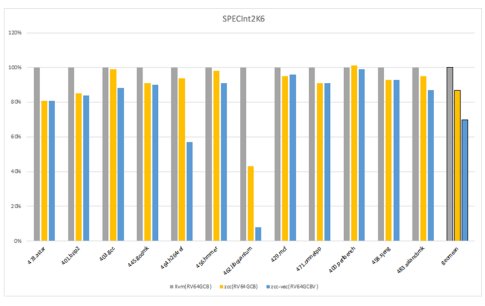

根据SPECInt2006动态指令数测试结果,相较开源LLVM 16.0,ZCC针对RISC-V RV64GCBV处理器的优化减少指令数30%,针对RISC-V RV64GCB处理器的优化减少指令数13%;

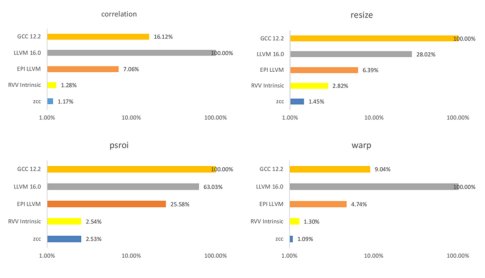

根据典型AI算子动态指令数结果,兆松科技ZCC工具链自动向量化性能相较于开源编译器最高提升91倍,意味着ZCC工具链可以为AI芯片的开发带来前所未有的优势。相较手写算子库,在保证性能的同时,可以大幅度降低维护成本。

兆松科技CTO伍华林表示,「兆松科技从ZCC工具链全面支持AndeStar™ V5的指令集作为起点,将逐步和晶心科技建立更进一步的合作,除了从工具链的代码密度和性能等优势上,帮助AndesCore™ RISC-V CPU IP更具有竞争力,未来还将提供软硬件协同设计工具,虚拟模型性能仿真工具等,帮助晶心科技的客户,高效的设计出有竞争力的芯片。」

「很高兴看到兆松科技与晶心科技合作协助我们的共同客户,大幅优化发挥出RISC-V处理器的效能, 同时进一步缩减代码。」晶心科技总经理暨技术长苏泓萌博士表示,「RISC-V技术持续快速发展,我们期许持续拓展生态系为客户提供专业开发工具的支持,进一步保障客户的产品效能与竞争力。」

关于兆松科技

兆松科技(武汉)有限公司成立于2019年底,以编译器和仿真器为核心技术,是国内鲜有的软硬件协同设计基础软件公司。兆松科技产品和解决方案覆盖软硬件协同设计、车规安全检测工具、DSA及嵌入式开发工具、ROS操作系统四大领域。欢迎关注兆松科技官网https://www.terapines.com及微信公众号。

关于Andes晶心科技

晶心科技股份有限公司于2005年成立于新竹科学园区,2017年于台湾证交所上市 (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099)。晶心是RISC-V国际协会的创始首席会员,也是第一家推出商用RISC-V向量处理器的主流CPU供货商。为满足当今电子设备的严格要求,晶心提供可配置性高的32/64位高效能CPU核,包含DSP、FPU、Vector、超标量 (Superscalar)、乱序执行 (Out-of-Order)及多核系列,可应用于各式SoC与应用场景。晶心并提供功能齐全的整合开发环境和全面的软/硬件解决方案,可帮助客户在短时间内创新其SoC设计。截至2022年底,嵌入AndesCore™ 的SoC累积总出货量已达120亿颗。更多关于晶心的信息,请参阅晶心官网https://www.andestech.com。

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- Andes晶心科技与WITTENSTEIN high integrity systems (WHIS)合作 建构RISC-V处理器安全关键解决方案

- 晶心科技45系列扩展RISC-V高端8 Stage超标量处理器,在丰富的 RISC-V 生态系统中,综合高性能、高能效以及实时定性

- 晶心推出最新RISC-V处理器支持多核超纯量的45系列及具备L2快取控制器的27系列

- AndesBoardFarm提供SoC工程师透过远程在线FPGA开发板探索RISC-V处理器