DCD推出完全可配置的通用LCD / TFT显示控制器DX LCD32

Poland, Bytom -- November the 2nd, 2016 -- Digital Core Design, an IP Core provider and a System-on-Chip design house from Poland, has introduced the newest IP Core. The DBLCD32 IP Core is a fully configurable, universal LCD/TFT display controller, which supports a wide range of resolutions. Moreover, it enables both, horizontal and vertical parameters’ synchronization setup.

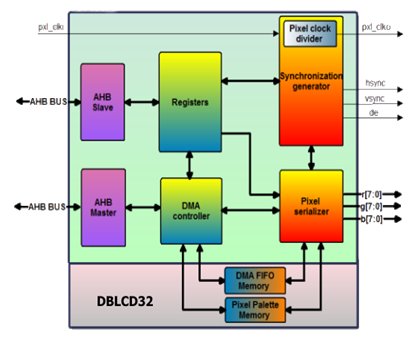

The DBLCD32 IP Core is a fully configurable, universal LCD/TFT display controller. It supports a wide range of resolutions and enables both, horizontal and vertical synchronization parameters setup. The display’s pixel clock can be generated by an internal pixel clock divider based on the bus clock, or delivered to the core by a dedicated pin.

"Additionally, an engineer can use an externally generated pixel clock" explains Tomasz Krzyzak, VP of DCD "Its polarization, as well as synchronization signals, is fully configurable".

The DBLCD32 has been also equipped with a DMA capable master interface, which can be used to access a framebuffer, when placed directly in a system memory. Embedded DMA controller has a configurable FIFO to store pixels data, which increases system throughput and performance.

"The transmission on the master interface is burst oriented and there is a possibility of defining the burst size limit" adds Krzyzak.

Data fetched by the DMA interface can be translated to 24-bits RGB signals, depending on the selected color mode. There are three standard color modes supported: 24-bits True Color, 16-bits(5-6-5) High Color and 8-bits index color mode. Additionally, a 32-bit True Color is also supported, but the MSB byte of each four byte word is ignored. In case of the Indexed Color Mode, the DBLCD32 is equipped with pixel palette RAM, which is used to translate each byte from the display buffer into 24-bit RGB output. There are two different formats of color palettes available. The core supports the page flipping mechanism, which enables the usage of multiple buffering without the tearing effect. The DBLCD32 incorporates also a set of programmable interrupts available related to both display synchronization and DMA status signals. The core is capable to work on both little and big endian systems. To increase the system performance and flexibility of usage, the DLBLCD32 can be configured in two possible optimization levels, to find a proper balance between a gate count and a critical path length.

More information: http://dcd.pl/ipcore/133/dblcd32/

Key features:

- 24-bit RGB interface,

- Configurable display resolution,

- Configurable horizontal sync length and blanking,

- Configurable vertical sync length and blanking,

- Configurable RGB signals polarization,

- Configurable pixel clock polarization,

- Internal pixel clock divider,

- Different pixel clock modes,

- DMA capable interface,

- Configurable DMA FIFO,

- Configurable burst size limit,

- AHB bus interface(32-bit)

- 24-bit True Color mode support,

- 16-bit (5-6-5) High Color mode support,

- 8-bit Indexed Color mode support,

- 32-bit True Color mode support (one byte ignored),

- Pixel palette RAM,

- Page flipping support,

- Programmable interrupts,

- Big and little - endian support,

- Two different optimization levels,

- Fully synthesizable, synchronous design.

Information about Digital Core Design:

The company founded in 1999, since the beginning stands in the forefront of the IP Core market. High specialization and profound customer service enabled to introduce more than 70 different architectures. Among them is the world’s fastest 8051 IP Core, the DQ80251, which is more than 75 times faster than the standard solution. The same, D32PRO, which is a royalty-free and fully scalable 32-bit CPU creates new possibilities for modern projects. As an effect, over 300 hundred licensees have been sold to more than 500 companies worldwide. Among them are the biggest enterprises like e.g. Sony, Siemens, General Electric and Toyota. But a lot of DCD’s customers are small businesses, R&D laboratories or front/back end offices, which require exact solution tailored to their project needs. Rough estimations say that more than 500 000 000 devices around the globe have been based on Digital Core Design’s IP Cores.

Related Semiconductor IP

Related News

- MIPI CSI 3、DSI 2 Tx/Rx高级控制器以及PHY IP内核现可支持主流Fab及工艺节点,适用于成像和显示应用SOC设计

- Digital Blocks 扩展其DB9000 TFT LCD、OLED 显示控制器及处理器 IP 在诸多应用领域的领军地位

- 电子显示器 端口 / 显示器端口 v1.4 Tx PHY 和控制器 IP 核心可用于 40nm ULP 和 12nm FFC,用于您的画面完美的 UHD、8K、4K 显示应用

- 适用于无延迟及纯超高清显示器的eDisplay Port/Display Port v1.4 Tx PHY 及控制器 IP 现可在40ULP 和 12FFC 工艺节点投入使用