Viterbi decoder (tail-biting)

The CMS0008 Viterbi Decoder core implements Viterbi’s algorithm for maximum likelihood decoding of non-feedback convolutional cod…

Overview

The CMS0008 Viterbi Decoder core implements Viterbi’s algorithm for maximum likelihood decoding of non-feedback convolutional codes.

The basic 1/2 rate convolutional encoder and decoder are shown above. For each input bit, two encoded bits are produced. The rate can be increased to 2/3, 3/4, 5/6, or 7/8 by non transmission (puncture) of certain bits. Punctured codes lose coding gain as the redundant content decreases.

The encoded X and Y bits are transmitted through a noisy channel. The received X and Y values are measured then presented as soft decision values to the decoder.

Burst-Mode Operation

Convolutional codes are fundamentally continuous processes and their use in burst-mode systems is problematic.

Many burst mode systems specify the use of known start- and end-states (typically zero) to correctly terminate the discontinuous data stream. However this requires insertion of non-payload termination symbols into the data stream, consuming valuable bandwidth.

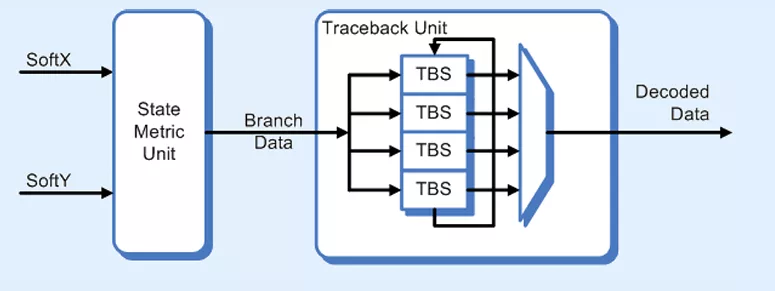

A description of the processing steps follows: State Metric Unit. This block maintains a measure of probability for each possible encoder state. As each soft pair is processed, the SMU produces the most likely received data bit for each state (the Branch Data vector).

Traceback Unit. This block provides a history of most likely state transitions. This allows traceback from any current state to ever more likely predecessor states.

After a certain depth the optimum state becomes known and traceback from this point produces reliable data. The required minimum traceback depth depends on the code parameters, puncture rate and soft-decision width. The alternative tail-biting strategy places data in the termination symbols, increasing the payload size at the cost of some additional decoder complexity.

While the additional complexity might seem daunting, the actual cost penalty is not high. Our tail-biting decoder provides comparable coding gain and group delay to typical zero-terminated decoders, with a moderate increase in gate count.

Key features

- Advanced Tail-Biting Architecture yields high coding gain and low delay.

- Synthesis configurable code generator coefficients and constraint length, soft-decision width and codeblock size.

- User-defined puncture patterns.

- Flexible memory architecture suitable for FPGA or ASIC

Block Diagram

Benefits

- Native rate 1/2 code with user-defined puncture

- Programmable constraint length and generator coefficients

- Zero latency between code blocks

- Fixed code block size

- Coding gain and group delay comparable to typical continuous-mode designs

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Our expertise is primarily in the gate- and power-efficient implementation of physical-layer (PHY) functions such as: modulation, demodulation, equalisation and channel coding but our experience encompasses all of the major elements of a modern baseband 'core' including the medium access control (MAC), voiceband DSP, mixed-signal interfaces, and embedded Cpu and software.

Our services are provided on a turnkey basis or as part of a support package attached to our licenced IP or tool products.

Commsonic's customers are typically semiconductor vendors and manufacturers of communications equipment that require leading-edge, Standards-based or proprietary PHY solutions but lack the internal resources or skills necessary to deliver projects against aggressive deadlines.

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is Viterbi decoder (tail-biting)?

Viterbi decoder (tail-biting) is a Channel Coding IP core from Commsonic Ltd listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.