Video Interlacer

The INTERLACER IP Core is a fully pipelined video interlacer solution that converts any progressive video format into its interla…

Overview

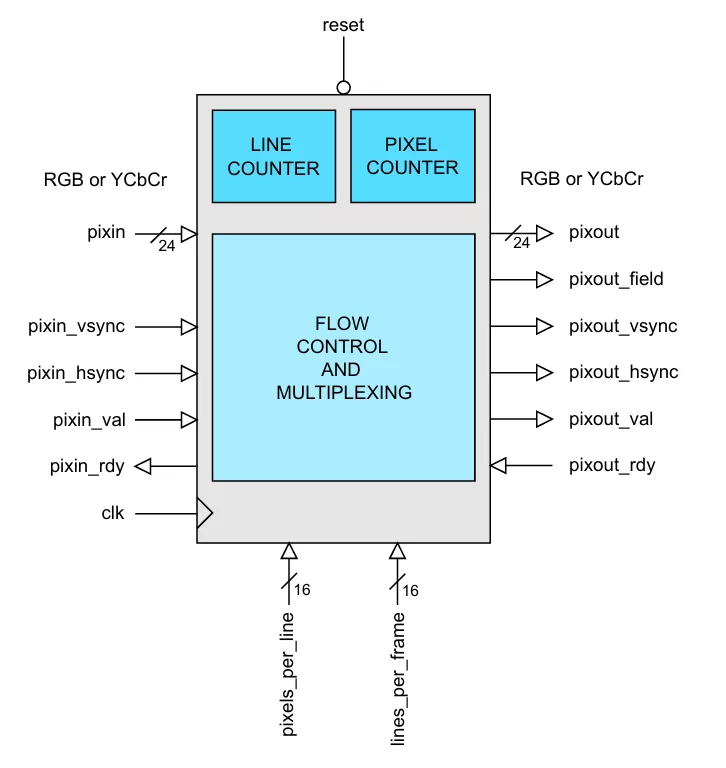

The INTERLACER IP Core is a fully pipelined video interlacer solution that converts any progressive video format into its interlaced equivalent. The format of the input video is defined by the parameters pixels_per_line and lines_per_frame. These values specify the size of one input frame of video in pixels and lines. Each interlaced output field will have half the number of lines as an input frame.

The input and output interfaces are streaming interfaces that follow a simple valid-ready pipeline protocol1. Input pixels and syncs are sampled on the rising edge of clk when pixin_val and pixin_rdy are both high. Likewise, output pixels and syncs are sampled on the rising edge of clk when pixout_val and pixout_rdy are high. The interfaces are compatible with all Zipcores video IP Cores and allow for easy connectivity between modules.

The input sync signals vsync and hsync are sideband flags that are coincident with the first pixel of a frame and the first pixel of a line respectively. The output sync signals are coincident with the first pixel of an output field. Note that the output interface has an additional field flag that identifies whether the field is odd or even. This field flag is held high or low for the duration of the output field.

Note that if no flow control is required in the design and the output is guaranteed to accept pixels without stalling, then the signal pixout_rdy may be tied high and the signal pixin_rdy may be ignored.

Key features

- Synthesizable, technology independent IP Core for FPGA, ASIC and SoC

- Supplied as human readable VHDL (or Verilog) source code

- Video interlacer converts any progressive video format to its interlaced equivalent – e.g. 1080p to 1080i

- Supports 24-bit RGB or 4:4:4 YCbCr pixels

- Supports all video resolutions up to 216 x 216

- Fully pipelined architecture with simple valid-ready flow control

- Self-flushing design operates like a simple FIFO

- One frame in generates one interlaced field out

- Output rate is one pixel per clock

- Supports 300 MHz+ operation on basic FPGA devices

Block Diagram

Applications

- Conversion of all standard and custom video formats such as 1920x1080p to 1920x1080i, 720x480p to 720x480i etc.

- Video solutions for flat panel displays, portable devices, video consoles, video format converters, set-top boxes, digital TV etc.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is Video Interlacer?

Video Interlacer is a Video Processing IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.