General-purpose & Specialized Ring PLLs + RTL-based Solutions

Silicon Creations’ broad portfolio of general-purpose and optimized ring-based PLLs offer a wide range of clocking solutions.

Overview

Silicon Creations’ broad portfolio of general-purpose and optimized ring-based PLLs offer a wide range of clocking solutions. 500+ global customers rely on our proven IP and industry-leading support in over 750+ ICs fabricated on millions of wafers. Our PLL products are available in all major foundries and process nodes: Planar, FinFET and beyond.

Silicon Creations engineers design robust PLL architectures as well as a number of supplementary circuits that can be used to design the clocking system for modern-day SoCs.

General-purpose PLLs:

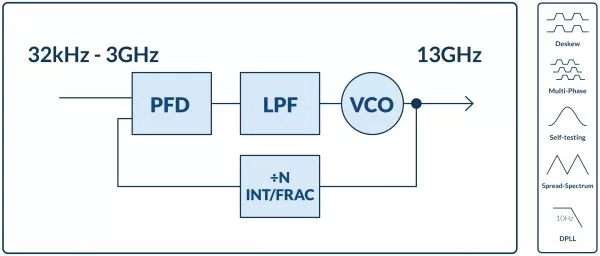

- Fractional-N PLL is a multi-function, general purpose frequency synthesizer. Ultra-wide input and output ranges along with excellent jitter performance, modest area, and application-appropriate power allow the PLL to be configured for almost any clocking application of complex SoC environments.

Optimized designs include:

- Low-Area Integer (or Low-Power) PLL that contains only crucial components and in some cases, no delta-sigma modulator. This PLL architecture lends itself to a high FoM with respect to period jitter while being roughly 4x smaller than general-purpose Fractional-N PLL.

- Low-Bandwidth PLL (IoT) is capable to operate with very low frequency reference (e.g. 32kHz) and achieve sub-mW power consumption. Provides VCO (and output) frequencies, on the order of tens or hundreds of MHz, enabling operation for many digital circuits.

- Low-Jitter PLL is the ultimate-performance ring-oscillator based circuit, achieving best-in-class sub-ps RMS long-term jitter and period jitter performance. Both Integer-N and Fractional-N modes are suitable for clocking precision data converters and SerDes, yet using a fraction of the die area needed for a traditional LC-PLL.

- For designs that call for the lowest possible jitter and higher oscillation frequencies, Silicon Creations’ LC-PLL circuits can be employed.

- Deskew PLL: Applicable for DDR interfaces and zero-delay buffer applications. Ability to work with high reference clock frequencies (e.g. 1600MHz), and can successfully track fast reference clock phase drift due to high loop bandwidth.

- Multi-phase PLL provides from 4 up to 16 or even 32 outputs with accurately spaced phase suitable for phase alignment in source-synchronous data interfaces like DDR2, DDR3 and DDR4.

RTL-based Solutions:

- Spread-Spectrum Modulator RTL IP provides industry-standard and custom modulation patterns for Silicon Creations fractional-N PLLs.

- Fully integrated Jitter Attenuator (Jitter Cleaner) RTL IP supplements PLLs to be used for Clock De-spreading, PON, OTU and Synchronous Ethernet applications with bandwidth programmable to below 1Hz.

- Jitter Monitor RTL IP allows on-chip clock jitter and duty cycle measurements.

- Digital Phase Aligner: An RTL IP that supplements the Fractional-N PLL to align clocks' phases and to track low-frequency phase variations.

Key features

- Application-optimized PLL Portfolio

- Industry Leading Production 3nm and above

- 0.01ppm Resolution, 24-bit Fractional Modulator with Near-integer Performance

- Excellent Results in Mass Production

- Silicon-accurate Simulation Models

Block Diagram

Benefits

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- PLL can be programmed while running to optimize for lowest jitter or lowest power - Programmable to use less than 1mW for less demanding clocks, yet can also be programmed to generate a PCIe1/2/3 compliant spread-spectrum reference clock or DDR 6400 reference.

- Low area on chip -- keepouts = DRC limit in most cases

- No external components required

- No additional supply decoupling required

- Self biased and automatically adjusts for any input frequency, so no complicated programming is required

What’s Included?

- GDSII

- CDL Netlist (MG Calibre Compatible)

- Functional Verilog Model

- Liberty timing models (.lib)

- LEF

- Application Note

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is General-purpose & Specialized Ring PLLs + RTL-based Solutions?

General-purpose & Specialized Ring PLLs + RTL-based Solutions is a PLL IP core from Silicon Creations listed on Semi IP Hub.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.