V-by-One® HS Tx IP / V-by-One® HS Rx IP

High-speed serial interface compliant with V-by-One® HS standard V-by-One® HS IP is an IP to achieve V-by-One HS high-speed video…

Overview

High-speed serial interface compliant with V-by-One® HS standard

V-by-One® HS IP is an IP to achieve V-by-One HS high-speed video interface technology. V-by-One® HS is a standard for next-generation high-speed interface technology developed by THine Electronics for image and video equipment requiring higher frame rates and higher resolutions. Implementing the V-by-One HS IP in Altera FPGA reduces the number of signals compared with conventional LVDS interfaces, which greatly reduces product cost.

Specifications

| Transmitter IP | Receiver IP | |

|---|---|---|

| Lane | 1~32 | |

| Pixel Data | 24,32,40 bit | |

| Self Test Function | FieldBET Pattern Generator | FieldBET Pattern Checker |

Supported Devices

- Intel® Agilex™ 7(F Tile)

- Intel® Stratix® 10 GX( H/L Tile )

- Intel® Arria® 10 GX

- Intel® Cyclone® 10 GX

Example Resource Utilization (Intel® Arria® 10 GX)

- RX

| 2Lane | 4Lane | 8Lane | 32Lane | |

|---|---|---|---|---|

| ALMs | 2,419 | 4,640 | 9,262 | 37,265 |

| registers | 4,977 | 9,956 | 19,914 | 79,309 |

- TX

| 2Lane | 4Lane | 8Lane | 32Lane | |

|---|---|---|---|---|

| ALMs | 1,531 | 3,067 | 6,709 | 24,542 |

| registers | 2,814 | 5,567 | 11,276 | 45,076 |

Key features

- Achieves 4-Gbps maximum transmission rate per lane (however, depends on the FPGA used)

- Supports custom video formats as well as VESA, SMPTE, and other standardized formats

- Supports flexible multi-lane designs in accordance with user's total transmission rate requirement

- Self-check function (FieldBET) to test connectivity between transmitter and receiver IPs

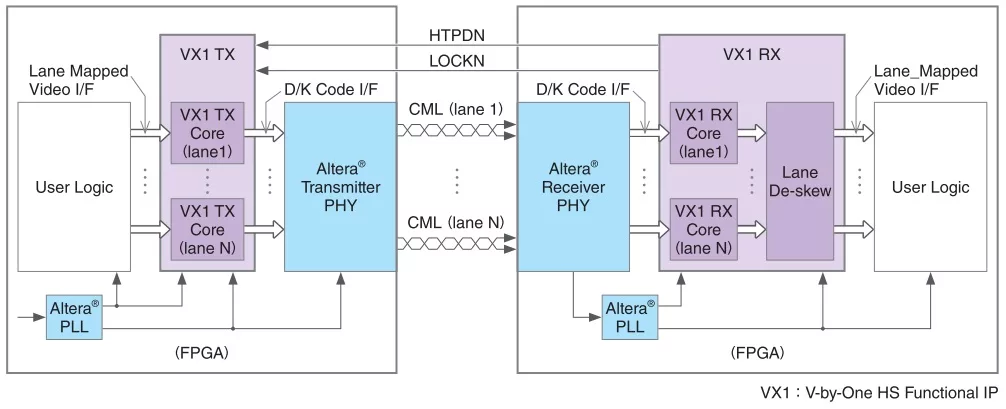

Block Diagram

What’s Included?

- Encrypted RTL (Verilog HDL)

- Reference design

- Simulation environment (For ModelSim)

- User's manual

- Reference design user's guide

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about V-By-One IP core

Frequently asked questions about V-by-One IP cores

What is V-by-One® HS Tx IP / V-by-One® HS Rx IP?

V-by-One® HS Tx IP / V-by-One® HS Rx IP is a V-By-One IP core from Macnica listed on Semi IP Hub.

How should engineers evaluate this V-By-One?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this V-By-One IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.