Simulation VIP for USB4

Used by all top market leaders semiconductor companies.The Cadence® Verification IP (VIP) for USB4 provides a capable verificatio…

Overview

Used by all top market leaders semiconductor companies.

The Cadence<sub>®</sub> Verification IP (VIP) for USB4 provides a highly capable verification solution for the USB4 protocol incorporating bus functional model (BFM) and integrated protocol checkers and coverage. It is based on the next-generation USB protocol architecture of USB4 specification. The VIP for USB4 enables multiple simultaneous data and display protocols and supports them to share the bandwidth over the bus. It supports two-lane operation and up to 40Gbps speed in USB4 Version 1.0 and up to 80Gbps in USB4 Version 2.0.

The VIP for USB4 is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

Supported Specifications: USB4 Specification Version 2.0 and 1.0, and USB4 Re-Timer Specification Version 1.0.

Key features

- Logical Layer

- Sideband channel

- Logical Layer State Machine

- GEN2, GEN3, and GEN4 speeds

- Lane initialization and link training

- Reed-Solomon forward error-correction code (RS-FEC)

- Dual-lane skew

- PAM3 encoding and decoding

- Low-power states

- Sleep and wake

- Asymmetric link entry and exit

- Error cases and recovery

- Interoperability with Thunderbolt 3 (TBT3) for Logical Layer

- Transport Layer

- Transport layer packets

- Routing

- Quality of service (QOS): Flow control schemes, bandwidth arbitration and priority

- Path setup and path tear-down

- Configuration Layer

- Router states

- Control packet protocol

- Router enumeration

- Hot plug and hot unplug events

- Time Synchronization

- Intra-domain and inter-domain time sync

- Bi-directional and uni-directional state machines

- Inversed bi-directional and adaptive uni-directional modes

- Serial time link protocol

- Configuration Spaces

- Support to read and write the defined configuration space for router, adapter, and path

- Support to backdoor access the configuration space

- USB3 Tunneling

- USB3 Gen X and Gen T adapters

- USB3 adapter layer encapsulation

- Path setup and tear-down

- Isochronous Timestamp Mechanism

- DP Tunneling

- LTTPR and non-LTTPR mode

- DP-IN and DP-OUT adapters

- DP adapter states

- System flows

- AUX request and response handling

- Intra-hop aux

- Set config, link training for 8b/10b and 128b/132b

- DP link clock sync

- 8b/10b SST tunneling

- 8b/10b MST tunneling

- 128b/132b tunneling

- DP FEC

- HDCP

- DP panel replay tunneling optimization for 8b/10b and 128b/132b tunneling

- PCIe® Tunneling

- PCIe adapter layer encapsulation

- Any max packet size

- Extended encapsulation

- Path setup and tear-down

- Precision time management (PTM) mechanism

- Re-Timer

- Sideband channel

- Re-timer channel state machine

- Low power

- Clock switching

- Interoperability with Thunderbolt 3 (TBT3) compatibility

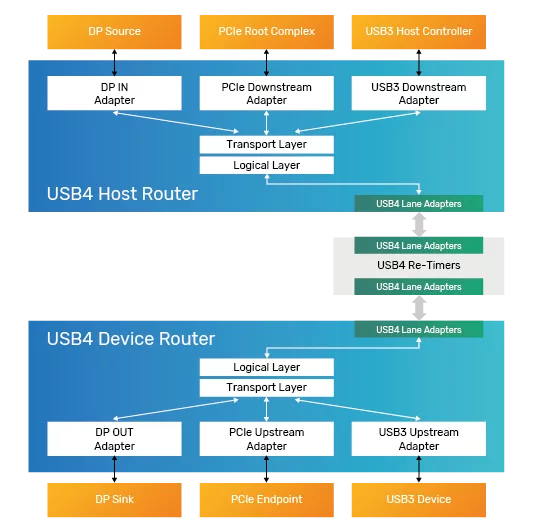

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is Simulation VIP for USB4?

Simulation VIP for USB4 is a USB IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.