eUSB2 v1 Verification IP

The eUSB2-v1 Verification IP provides an effective & efficient way to verify the components Supporting eUSB2-v1 Revision 1.2 Spec…

Overview

The eUSB2-v1 Verification IP provides an effective & efficient way to verify the components Supporting eUSB2-v1 Revision 1.2 Specification The eUSB2-v1 VIP is fully compliant with standard eUSB2-v1 specifications from USB-IF. This VIP is a lightweight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key features

- Supports eUSB2-v1 Low-Speed,Full-Speed and High-Speed Bus State Representaons.

- Supports all encoding of eUSB2-v1 Control Message (CM) Signaling for nave and repeater mode configurations.

- Supports the Disconnect/Connect with Digital Ping in Full/Low speed & Analog Ping with High-Speed Signaling at nave and repeater modes.

- Supports Protocol Extended Token transactions for LPM Ack handshake.

- Supports all eUSB2-v1 Repeater architecture and operations Host Reset, Low power states, Resume, Remote Wakeup, Disconnect Signaling between Host and Peripheral device.

- Compliant with eUSB2-v1 specification rev 1.2.

- eUSB2-v1 PHY and eUSB2-v1 is fully compliant to the USB2.0 Rev 2.0 Specificaon that supports high, full, & low-speed operation.

- Supports any eUSBV1 device in nave mode.

- Supports USB 2.0 operation based on repeater architecture.

- Supports UTMI/UTMI+ Parallel Mode.

- Supports link power management LPM-L1 (L1) and Suspend (L2).

- Supports register access protocol (RAP) for eUSB2-v1 device or repeater configurations.

- Fully compliant to USB2.0 base spec at the protocol layer.

- Fully compliant to the USB2.0, xHCI 1.1, Utmi+ 1.0 Transceiver Interface Specificaon with backward compality to USB 1.1.

- Supporting On-The-Go which is fully compliant with OTG Rev 2.0, V1.1a.

- Supports xHCI functionality on the Host model.

- Host Model Supports up to 127 devices of any tier level.

- Supports 15 IN and 15 OUT and 1 control endpoint for each device.

- User-controlled device aach/ detach function.

- Supports High Speed, Full Speed, and Low-Speed Functionality.

- Programmable SOF generation time.

- Supports all USB2 transfer types; Control, Bulk, Interrupt, and Isochronous.

- Supports High Bandwidth ISO and Interrupt transfers.

- Supports resume and remote wake-up.

- Configurable Utmi+ Interface width 8 and 16 bits.

- Supports randomisation for packet fields and data payload with or without error injection.

- Comprehensive Compliance Test Suite for verification.

- Supports all types of error injection (control transfer (Request error), PID, CRC, Interpacket Delay, Sync, EOP, Bitstuff etc.) and detection.

- Supports detailed activity log files for individual layers for Debugging.

- Supports dynamically configurable modes.

- Strong Protocol Monitor with real time exhaustive programmable checks.

- Supports configuring Protocol Timers and intenonally error masking.

- On the fly protocol checking using protocol check functions, and assertion checks for UTMI Interface.

- Built-in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Host and Device.

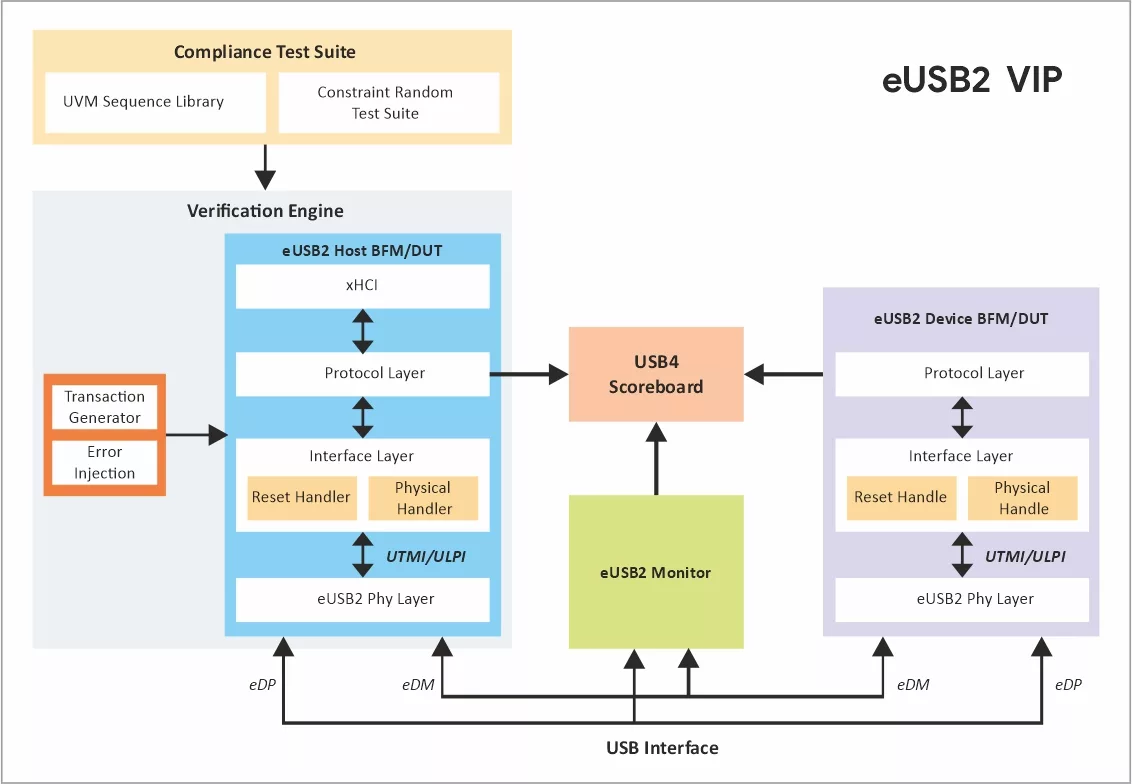

Block Diagram

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest levels of quality

- 24x5 customer support & response under 90 Min.

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

What’s Included?

- eUSB2-v1 HOST/DEVICE/REPEATER BFMs

- eUSB2-v1 Bus Monitor, Protocol Monitor and Scoreboard.

- BFM Agents for:

- 1 Protocol Layer

- 1 PHY Layer

- Compliance Test Suite (CTS)

- Stress test for each standard layer

- xHCI VIP compatible with Revision 1.2

- Integration Guide, User Manual and Release Notes

- GUI analyser to view simulation packet flow

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is eUSB2 v1 Verification IP?

eUSB2 v1 Verification IP is a USB IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.