Overview

The RapidIO Interconnect Architecture is an industry-standard, packet-based interconnect technology that provides a reliable, high-performance interconnect between NPUs (network processing units), CPUs (central processing units), and DSPs (digital signal processors). Serial RapidIO enables chip-to-chip, board-to-board, and system-to-system communications and is targeted at the networking, embedded, and storage markets. RapidIO has won broad acceptance in wireless infrastructure applications, where it is used as a primary interconnect for DSP clusters in baseband processing.

Evaluate SRIO 2.1 IP Core With AMC Evaluation Platform LatticeECP3 AMC Demonstration Kit consists of

* LatticeECP3 AMC Evaluation board

* Associated cables

* AMC interface card

* Demonstration bitstreams and files

Learn more about RapidIO IP core

Eric Esteve

Designers have many different options for implementing a RapidIO interconnect. This article outlines the decision factors that designers should consider, organized by project development phases: system design, implementation, system verification, and system evolution. A last section discusses support services, which impact all stages of project development.

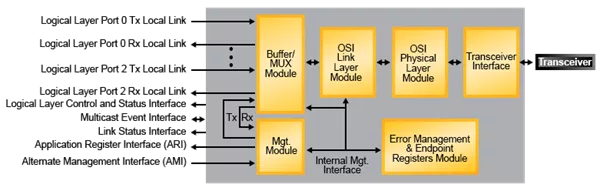

RapidIO is an open, standards-based interconnection technology for midsize and large embedded systems. It enables packet-switched, peer-to-peer connections among ASICs, DSPs, FPGAs, microprocessors, network processors and backplanes, with speeds of up to

RapidIO moves up to Fabric

Enter the Inner Sanctum of RapidIO: Part 1

Enter the Inner Sanctum of RapidIO: Part 2