SENT (SAE J2716) Verification IP

Single Edge Nibble Transmission (SENT) is a single-wire, serial unidirectional communication protocol.

Overview

Single Edge Nibble Transmission (SENT) is a single-wire, serial unidirectional communication protocol. It is intended for use in applications where high resolution sensor data needs to be communicated from a sensor to an Engine Control Unit (EUC). It is intended as a replacement or the lower resolution methods of 10 bit A/D's and as a simpler low cost alternative to CAN or LIN in automotive industry. SENT (SAE J2716) Verification IP are reusable components that provide ready made verification environment. Compatible with Single Edge Nibble Transmission (SENT) specifications and supports all the frame types. SENT (SAE J2716) includes an extensive test suite covering most of the possible scenarios. It can perform all protocal tests and moreover it allows an easy generation of very high number of patterns and a set of specified patterns to stress the DUT.

SENT (SAE J2716) Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SENT (SAE J2716) Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Compatible with Single Edge Nibble Transmission (SENT) specification SAE J2716 April 2016

- Supports SENT/SPC protocol as defined in the MPC5510 Microcontroller family (AN4219)

- Supports both SLOW and FAST channel transmissions.

- Supports following types of frame formats in SLOW channel transmission.

- Short Serial Message format

- Enhanced Serial Message format

- Enhanced serial message formats Supports different configurations

- 12-bit data and 8-bit message ID

- 16-bit data and 4-bit message ID

- These SAE J2716 nodes can be configured as Sensor, Active Device or Passive Device nodes.

- The DUT can either be a SAE J2716 sensor or device.

- Supports following types of frames formats in FAST channel transmission.

- H.1: Two 12-bit fast channels (6 data nibbles).

- H.2: One 12-bit fast channel (3 data nibbles).

- H.3: High-speed with one 12-bit fast channel (4 data nibbles, where only values 0-7 are used).

- H.4: Secure sensor with 12-bit fast channel 1 and secure sensor information on fast channel 2 (6 data nibbles).

- H.5: Single sensor with 12-bit fast channel 1 and zero value on fast channel 2 (6 data nibbles).

- H.6: Two fast channels with 14-bit fast channel 1 and 10-bit fast channel 2 (6 data nibbles).

- H.7: Two fast channels with 16-bit fast channel 1 and 8-bit fast channel 2 (6 data nibbles).

- Supports programmable clock frequency of operation.

- Supports all types of error insertion and detection

- Checksum error

- Message ID error

- Oversize error

- Sync error

- Supports pause pulse properties

- Minimum length 12 ticks

- Maximum length 768 ticks

- Built-in checkers ensures that SENT (SAE J2716) Protocol has been followed correctly.

- Allows creation of both random and directed testcases.

- Functional coverage for complete SENT (SAE J2716) features.

- Supports callbacks in monitor, device and sensor BFMs for user processing of data.

- Monitors, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations.

- SENT (SAE J2716) Verification IP comes with complete testsuite to test every feature of SENT (SAE J2716) specification.

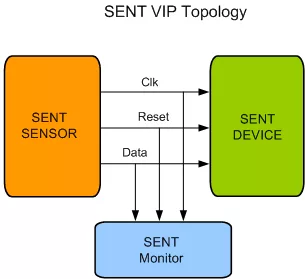

Block Diagram

Benefits

- Faster testbench development and more complete verification of SENT (SAE J2716) Verification IP designs.

- Easy to use command interface simplifies testbench control and configuration of device and sensor.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the SENT (SAE J2716) Verification IP testcases.

- Examples showing how to connect various components, and usage of Sensor, Device and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SENT IP core

Integrating PQC into StrongSwan: ML-KEM integration for IPsec/IKEv2

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Accelerating PCIe Gen6 L0p Verification for AI & HPC Designs using Synopsys VIP

Morgan State University (MSU) Leveraging Intel 16 and the Cadence Tool Flow for Academic Chip Tapeout

UEC-LLR: The Future of Loss Recovery in Ethernet for AI and HPC

Frequently asked questions about SENT IP cores

What is SENT (SAE J2716) Verification IP?

SENT (SAE J2716) Verification IP is a SENT IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SENT?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SENT IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.