SATA HOST CONTROLLER IIP

SATA HOST CONTROLLER core is compliant with SATA version 3.5 specification.

Overview

SATA HOST CONTROLLER core is compliant with SATA version 3.5 specification. Through its compatibility, it provides a simple interface to a wide range of low-cost devices. SATA HOST CONTROLLER IIP is proven in FPGA environment. The host interface of the SATA can be simple interface or can be AMBA APB, AMBA AHB, AMBA AXI, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol.

SATA HOST CONTROLLER IIP is supported natively in Verilog and VHDL

Key features

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

- Scan test ready

- Simple interface allows easy connection to microprocessor/microcontroller

- devices

- Supports 1.5 Gbit/s, 3.0 Gbit/s and 6.0 Gbit/s data transfer rates

- Supports DMA and PIO commands

- Hardware support for

- 48-bit address set

- Detection of OOB, COMWAKE, K28.5, etc.

- 8b/10b coding and decoding

- CRC generation and checking

- Auto insertion of HOLD primitives

- Native Command Queuing (NCQ)

- Port Multiplier, Port Selector

- First Party DMA (FPDMA)

- CONT primitive support for primitive suppression to reduce EMI

- Implements the shadow register block and the serial ATA status and control

- registers

- Complete Link Layer state machine.

- Selectable data scrambling option.

- Supports link layer power modes.

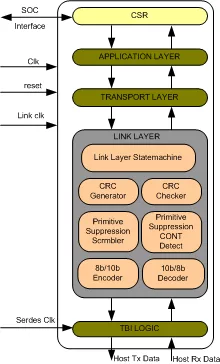

Block Diagram

Benefits

- Single site license option is provided to companies designing in a single site.

- Multi sites license option is provided to companies designing in multiple sites.

- Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

- Unlimited Designs, license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

What’s Included?

- The SATA Host Controller interface is available in Source and netlist products.

- The Source product is delivered in plain text verilog.If needed VHDL,SystemC code can also be provided.

- Easy to use Verilog Test Environment with Verilog Testcases

- Lint, CDC, Synthesis, Simulation Scripts with waiver files

- IP-XACT RDL generated address map

- Firmware code and Linux driver package

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SATA Controller IP core

Verification of USB 3.0 Device IP Core in Multi-Layer SystemC Verification Environment

Designing Around an Encrypted Netlist: Is The Pain Worth the Gain?

STBus complex interconnect design and verification for a HDTV SoC

Interface IP: Winners, Losers in 2013

The IP Paradox: Sales are growing despite Semi Consolidation

Frequently asked questions about SATA Controller IP

What is SATA HOST CONTROLLER IIP?

SATA HOST CONTROLLER IIP is a SATA Controller IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SATA Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SATA Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.