SAS Initiator, 12G, 4 Ports, 48 Gbps

The SAS Initiator Controller IP Core provides an interface to high-speed serial link replacement for the parallel SCSI attachment…

Overview

The SAS Initiator Controller IP Core provides an interface to high-speed serial link replacement for the parallel SCSI attachment of mass storage devices. Maximum supported bandwidth is 48 Gbps. The serial link employs multiple high-speed gigabit transceivers.

ARCHITECTURE

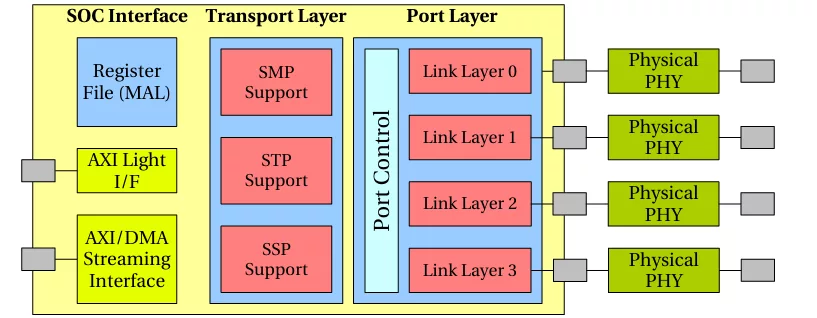

This high performance implementation of a SAS Initiator support every mandated feature outlined by the latest SAS Specification. The implementation is highly configurable, to provide the most flexibility and satisfy every need.

The design is cleanly partitioned in to the fundamental function blocks of a SAS Initiator:

- PHY (SERDES)

- PHY Layer

- Port Layer

- Link Layer

- SSP

- SMP

- SATA

- Transport Layer

- AXI Interface

We include a FPGA based PHY, or the IP Core can interface to a standard SAS PHY from a 3rd party. The FPGA based PHY is targeted for Xilinx series 7 devices, with GTX and GTH transceivers.

Our PHY includes all functions required to bring up the link all the way to 12G.

The SoC interface consists of a AXI Light interface to access internal registers, and a AXI 4.0 Streaming interface for data transfers. We have successfully tested this IP Core with the following SAS SSDs:

- HGST 200GB SAS12G SSD

- Seagate 200GB SAS12G SSD

- Toshiba 200GB SAS12G SSD

- Micron 100GB SAS6G SSD

- Talos (OCZ) 200GB SAS6G SS

Key features

- SAS & SATA Speed Negotiation and OOB

- SAS 1.5, 3.0, 6.0 and 12.0 Gbps support

- SATA 1.5, 3.0 and 6.0 Gbps support

- Native 32 bit PHY interface

- AXI SoC Interface

- Rate Tolerance Management

- Data and Idle scrambling

- Frame assembly and decoding

- Power Management

- Configurable, 1 quad, 2 dual or 4 single narrow, or 1 quad or 2 dual wide ports

- Automatic Identify and Reset Management

- Automatic Connection Control

- Support of SMP, SSP and native SATA protocols

- Multi-channel S/G DMA support with on-demand processing

- 256 bit DATA stream

- Multiple simultaneous connections per device

- Sustained 48 GBps bandwidth

- Up to 32 internal transmit buffers

- Up to 32 internal receive buffers

- Xilinx Transceiver based PHY

Block Diagram

Benefits

- Very fast, high performance implementation

- Small footprint

- Easy to use

Applications

- Mass storage

- Linux SoC

- Data Recorder

- Raid System

What’s Included?

- Verilog HDL Source Code

- Test bench

- Documentation

- Technical Support

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SAS IP core

Video: Cadence Demonstrates PCIe Gen3 Silicon at PCI-SIG Dev-Con (SAS RAID Controller)

Embedded Security explained: IPsec and IKEv2 for embedded Systems

ReGate: Enabling Power Gating in Neural Processing Units

Bringing IPsec into the Quantum Safe Era

The Benefits of a Multi-Protocol PMA

Frequently asked questions about SAS IP cores

What is SAS Initiator, 12G, 4 Ports, 48 Gbps?

SAS Initiator, 12G, 4 Ports, 48 Gbps is a SAS IP core from ASICS World Services, LTD. listed on Semi IP Hub.

How should engineers evaluate this SAS?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SAS IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.