QDR4 Synthesizable Transactor

QDR4 Synthesizable Transactor provides a smart way to verify the QDR4 component of a SOC or a ASIC in Emulator or FPGA platform.

Overview

QDR4 Synthesizable Transactor provides a smart way to verify the QDR4 component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's QDR4 Synthesizable Transactor is fully compliant with standard QDR4 Specification and provides the following features.

Key features

- Supports 100% of QDR4 protocol standard CY7C4142KV13

- Supports 144-Mbit density (8M × 18, 4M × 36)

- Supports eight-bank architecture enables one access per bank per cycle

- Supports two-word burst on all accesses

- Supports dual independent bidirectional data ports

- Supports double data rate (QDR4) data ports

- Supports concurrent read/write transactions on both ports

- Supports single address port used to control both data ports

- Supports QDR4 address signaling

- Supports single data rate (SDR) control signaling

- Supports high-speed transceiver logic (HSTL) and stub series terminated logic (SSTL) compatible signaling (JESD8-16Acompliant)

- Supports pseudo open drain (POD) signaling (JESD8-24 compliant)

- Supports programmable for clock, address/command, and data inputs

- Supports internal self-calibration of output impedance through ZQ pin

- Supports bus inversion to reduce switching noise and power

- Supports programmable on/off for address and data

- Supports address bus parity error protection

- Supports training sequence for per-bit de skew

- Supports on-chip error correction code (ECC) to reduce soft error rate (SER)

- Supports all the QDR4 commands as per the specs

- Supports full-timing as well as behavioral versions in one model

- Models, detects and notifies the test bench of significant events such as transactions, warnings, and timing protocol violations

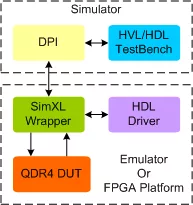

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the QDR4 testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SRAM IP core

Novel Trade-offs in 5 nm FinFET SRAM Arrays at Extremely Low Temperatures

Why SRAM PUF Technology Is the Bedrock of Dependable Security in Any Chip

AI-driven SRAM demand needs integrated repair and security

A comparison of SRAM vs quantum-derived semiconductor PUFs

Basics of SRAM PUF and how to deploy it for IoT security

Frequently asked questions about SRAM IP cores

What is QDR4 Synthesizable Transactor?

QDR4 Synthesizable Transactor is a SRAM IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SRAM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SRAM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.