QDR2 Synthesizable Transactor

QDR2 Synthesizable Transactor provides a smart way to verify the QDR2 component of a SOC or a ASIC in Emulator or FPGA platform.

Overview

QDR2 Synthesizable Transactor provides a smart way to verify the QDR2 component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's QDR2 Synthesizable Transactor is fully compliant with standard QDR2 Specification and provides the following features.

Key features

- Supports 100% of QDR2 protocol standard CY7C1314CV18

- Supports separate independent read and write data ports with concurrent read and write operation

- Supports full data coherency, providing most current data

- Supports synchronous pipeline read with self-timed late write

- Supports registered address, control and data input/output

- Supports QDR (quad data rate) interface on read and write ports

- Supports fixed 4-bit burst for both read and write operation

- Supports two input clocks (K and K) for accurate QDR timing at clock rising edges only

- Supports two input clocks for output data (C and C) to minimize clock-skew and flight-time mismatches

- Supports two echo clocks (CQ and CQ) to enhance output data traceability

- Supports single address bus

- Supports byte write function

- Supports simple depth expansion with no data contention

- Supports programmable output impedance

- Supports single multiplexed address input bus latches address inputs for both read and write ports

- Supports separate port selects for depth expansion

- Supports synchronous internally self-timed writes

- QDR II operates with 1.5 cycle read latency when delay lock loop (DLL) is enabled

- Operates similar to a QDR I device with one cycle read latency in DLL off mode

- Supports available in x18, and x36 configurations

- Supports variable drive HSTL output buffers

- Supports all the QDR2 commands as per the specs

- Supports delay lock loop (DLL) for accurate data placement

- Supports full-timing as well as behavioral versions in one model

- Models, detects and notifies the test bench of significant events such as transactions, warnings, and timing protocol violations

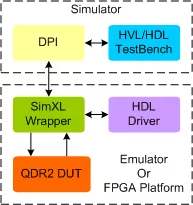

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV VIP's

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the QDR2 testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SRAM IP core

Novel Trade-offs in 5 nm FinFET SRAM Arrays at Extremely Low Temperatures

Why SRAM PUF Technology Is the Bedrock of Dependable Security in Any Chip

AI-driven SRAM demand needs integrated repair and security

A comparison of SRAM vs quantum-derived semiconductor PUFs

Basics of SRAM PUF and how to deploy it for IoT security

Frequently asked questions about SRAM IP cores

What is QDR2 Synthesizable Transactor?

QDR2 Synthesizable Transactor is a SRAM IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SRAM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SRAM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.