Processor Development Toolset

Codasip Studio is a set of Electronic Design Automation (EDA) tools for processor design and customization.

Overview

Codasip Studio is a complete set of Electronic Design Automation (EDA) tools for processor design and customization. The level of automation is unmatched on the market, and produces fast and efficient results.

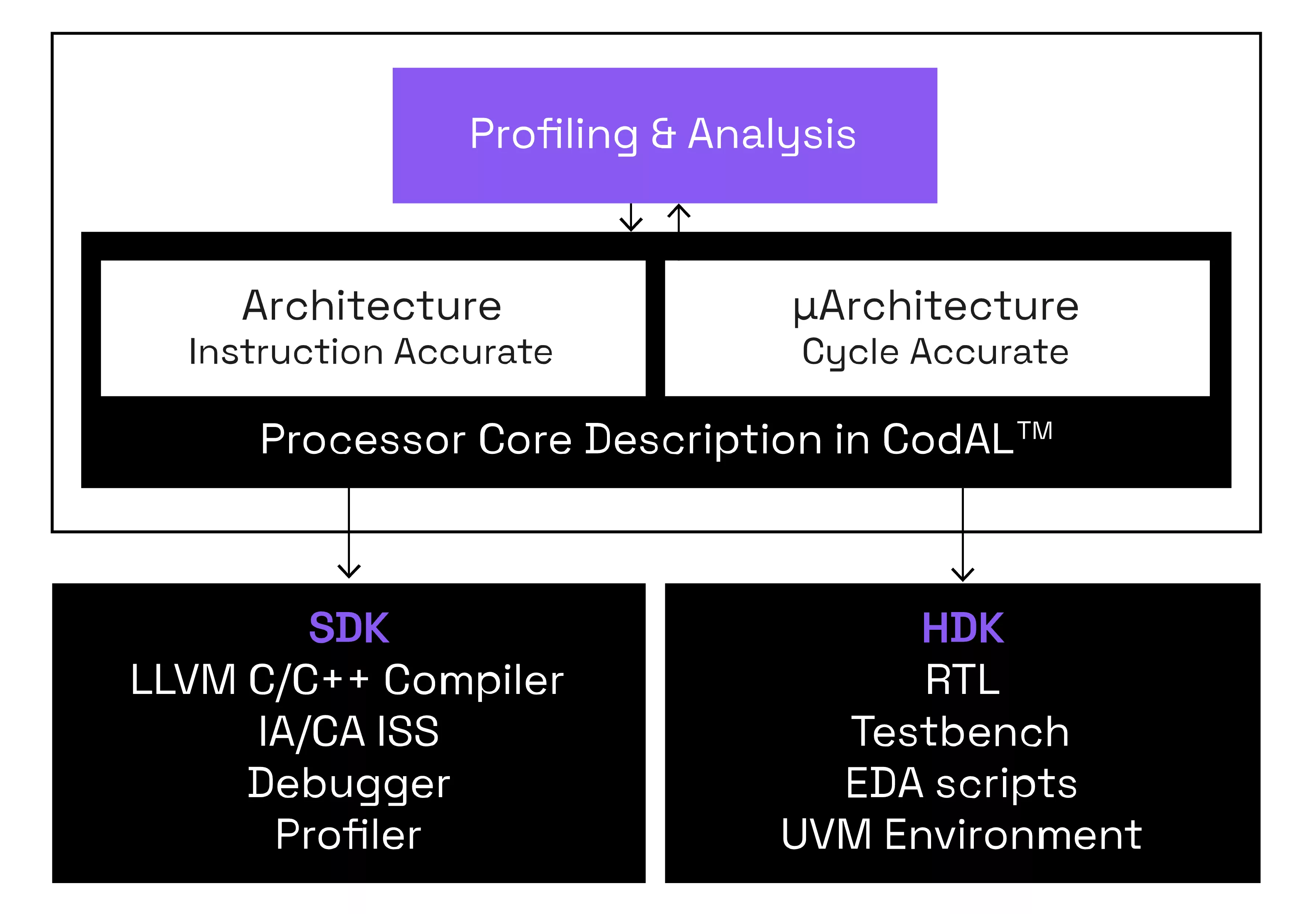

Our approach at Codasip is to automate the development of processor cores by using a high-level description in the CodAL processor description language and generating the design implementation, verification environment, virtual system prototype, and a complete software toolchain using Codasip Studio.

In addition to its design capabilities, Codasip Studio includes powerful multiprocessor programming, debugging and profiling features, enabling the development of complex processor designs with ease.

Codasip Studio is built upon open standards and software including Eclipse, LLVM, Verilog, SystemVerilog, and UVM.

Key features

- A unified development model describing the processor in a single CodAL description

- High performance processor synthesis

- Complete UVM verification environment

- Advanced profiling and analysis

- Compatible with Codasip RISC-V cores

Block Diagram

Benefits

- By creating a high-level processor description in CodAL and automatically generating virtual prototypes, an SDK, RTL and a verification environment there is hugely reduced design time and cost.

- CodAL allows adding application-specific instructions natively to the processor pipeline well above traditional processor extensible approaches.

- Once an instruction-accurate model of the processor is available it is possible to generate an SDK to allow embedded software teams to develop, debug and test their code well ahead of silicon availability.

- Codasip Studio generates human readable RTL.

- A generated SystemVerilog UVM environment allows verification of the RTL against an instruction accurate reference model.

Applications

- Any form of customizing Codasip RISC-V cores developed using Studio such as creating custom instructions.

- Creating special processor architectures for specialized applications such as security, DSP, AI or imaging

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Processor Development Toolset?

Processor Development Toolset is a CPU IP core from Codasip listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.