PHY for PCIe 4.0 - Low-power, long-reach, multi-protocol PHY for PCIe 4.0

The 16G Multi-Link and Multi-Protocol PHY is a silicon-proven, high-end SerDes operating at speeds from 1.25Gbps to 16Gbps featur…

Overview

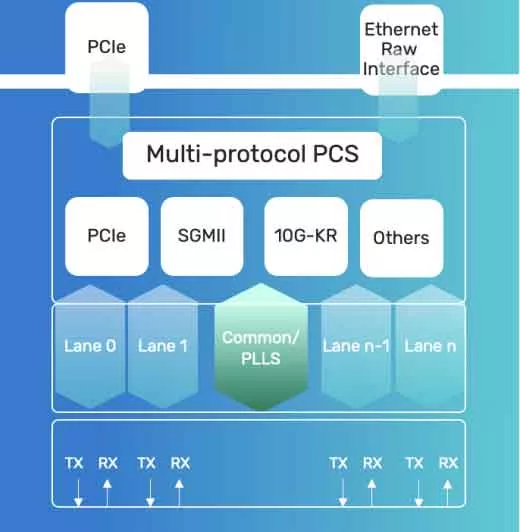

The 16G Multi-Link and Multi-Protocol PHY is a silicon-proven, high-end SerDes operating at speeds from 1.25Gbps to 16Gbps featuring long-reach equalization capability at very low active and standby power. This SerDes offers ultra-low exit latency for time-critical applications. It simultaneously supports PCI Express® (PCIe®) 4.0, 10G-KR, and QSGMII/SGMII, and other protocols allowing great flexibility to mix and match protocols within the same macro.

Key features

- Wide range of protocols that support networking, high-performance computing (HPC), and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- User-friendly graphical interface provides easy access to embedded bit-error-rate (BER) and pattern testers and monitors to measure the link performance in real time

- Extensive set of isolation, test modes, and loop-backs including APB and JTAG

- Supports 16-bit, 20-bit, and 32-bit PIPE and non-PIPE interfaces

- Selectable serial pin polarity reversal for both transmit and receive paths

Block Diagram

What’s Included?

- PMA Hard Macro

- PCS-BIST Soft Macro

- Datasheet

- SoC integration guide

- Optional design integration and bring-up support services

Specifications

Identity

Standards & Interfaces

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is PHY for PCIe 4.0 - Low-power, long-reach, multi-protocol PHY for PCIe 4.0?

PHY for PCIe 4.0 - Low-power, long-reach, multi-protocol PHY for PCIe 4.0 is a Single-Protocol PHY IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.