PCI Express Synthesizable Transactor

PCIE Synthesizable Transactor provides a smart way to verify the PCIE component of a SOC or a ASIC in Emulator or FPGA platform.

Overview

PCIE Synthesizable Transactor provides a smart way to verify the PCIE component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's PCIE Synthesizable Transactor is fully compliant with standard PCIE Specification and provides the following features.

Key features

- Supports PCI Express specs 1.0/2.0/3.0/4.0/5.0/6.0.

- Supports MPCIE

- Supports PIPE, PCS/PMA, and serdes interface

- Supports MPHY RMMI and serial Interface

- Supports all error injections in MPHY layer

- Supports all protocol checks for MPHY layer

- Supports all PWM and HS gears as supported by MPCIE

- Supports all lane configurations as supported by MPCIE

- Supports automatic clock recovery for HS mode

- Supports asymmetrical lane configuration

- Supports dynamic bandwidth scalability as per specs

- Supports both Rate A and Rate B

- Supports UVM and Verilog APIs supplied, as well as C DPI exports

- Supports Gen 1, 2, 3, 4, 5 and 6 including SSC

- Supports full link speed and width negotiation up to 32 Lanes

- Supports automated Error Injections at all layers

- Checkers verify protocol timing checks and functional accuracy at each layer

- Supports queuing for 8 VCs with configurable depth

- Configurable TC to VC queue mapping

- Multiple Requester / Completer applications, including user supplied applications

- User interface for direct TLP queuing and receipt

- Check all TLPs for correct formation of headers, prefixes, and ECRC

- Supports full DL state machines

- Check all framing, LCRC, and lane rules

- Check all DLLP fields and formatting

- Interface to send / receive user defined DLLPs

- Supports ASPM and Software controlled Power Management

- Supports automated Error Injections and checking

- Supports full LTSSM state machine

- Supports serdes model with digital clock recovery

- Supports speed and Link Width negotiation

- Supports Up configure, polarity inversion, and lane-to-lane skew

- Configurable Spread Spectrum Clocking (SSC)

- Supports gen 1 and gen 2 PCS, 8b/10b encoding

- Supports gen 3, gen 4 and gen 5 128b/130b encoding

- Supports gen 6 flit based encoding.

- Configurable timers and timeouts

- Supports scaled Flow Control

- Supports data Link Feature Exchange

- Supports lane Margining at Receiver

- Supports vF 10-Bit Tag Requester

- Supports enhanced Allocation

- Supports emergency Power Reduction State

- Supports fully synthesizable

- Supports static synchronous design

- Supports positive edge clocking and no internal tri-states

- Supports simple interface allows easy connection to microprocessor/microcontroller devices

- Compliant with PIPE 5.2.1 Specification

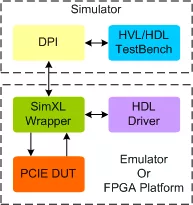

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the PCIE testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about PCI Express IP core

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Complete Interface Solution for PCI Express 5.0 Launched

Doubling Bandwidth in Under Two Years: PCI Express Base Specification Revision 5.0, Version 0.9 is Now Available to Members

Frequently asked questions about PCIe IP cores

What is PCI Express Synthesizable Transactor?

PCI Express Synthesizable Transactor is a PCI Express IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.