Overview

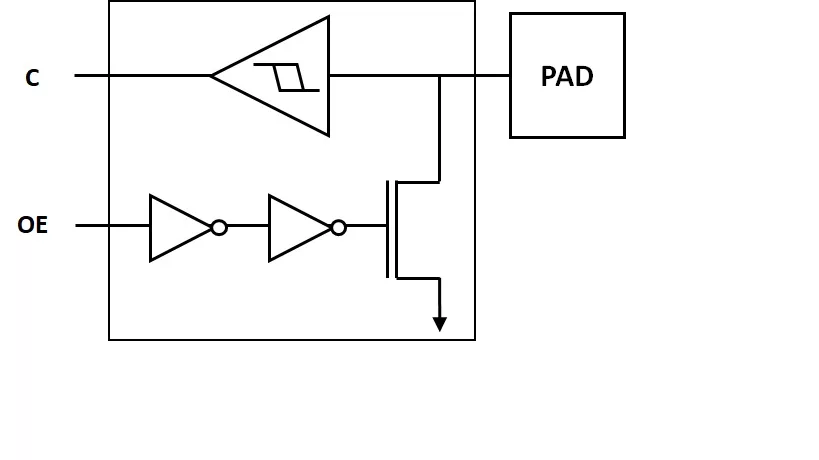

Certus is pleased to offer I2C open-drain IOs across multiple process technologies. The Certus I2C IO can support external supplies of 1.8V, 3.3V and 5V at Fast Mode (400Kbps) and Fast Mode+ (1Mbps) data rates. The Certus solution features power sequence independence, a hysteresis input, and true fail-safe operation. Fully compatible with the Certus GPIO library, this cell can be configured across a broad range of open-drain interfaces, resistive and capacitive loads. Our Open Drain IO solutions are also SMBUS, DDC, CEC and HPD compliant.

Built into our IO libraries, and also offered as a separate service, is our strong ESD expertise. Certus was founded by ESD engineers and our results speak for themselves. Not only do we consistently exceed the standard ESD targets of 2KV HBM and 500V CDM, but we also provide on-chip solutions for standards such as IEC-61000-4-2, system-level ESD and Cable Discharge Events (CDE).

Certus also offers RGMII, Secure Digital, LVDS, Analog/RF, HV and numerous other IO variants across most major foundries and technology nodes. We are particularly suited at providing customized options in a cost-efficient framework. Please contact us for supplementary physical or electrical features that can suit your needs.

Learn more about GPIO IP core

For over a decade, Sofics has collaborated with CERN, the European Organization for Nuclear Research. Sofics has delivered advanced GPIO cells tailored for radiation-hardened applications, supporting CERN’s groundbreaking particle physics experiments.

This paper provides a complete solution to the GPIO Verification for any SoC. GPIO interface is available in every ASIC. To avoid duplicate efforts and (save) time to verify the GPIO interface, we have produced this Generic GPIO verification suite. It is a UVM-based verification environment, with all the necessary subcomponents that are required to verify any GPIO design.

Post-quantum cryptography (PQC) is moving from theory to engineering reality. With NIST-standardized algorithms ML-KEM (FIPS 203) and ML-DSA (FIPS 204) now finalized, FPGA developers face a practical challenge: How to integrate these algorithms efficiently on resource-constrained hardware?

The I2C (Inter-Integrated Circuit) Bus invented in 1980 by Philips Semiconductors (NXP Semiconductors today) was a massive step forward in simplifying communications in embedded systems. It is a simple two-wire interface for synchronous, multi-master/multi-slave, single ended serial communication. Fast forward 45 years to today and it is still widely used for attaching low speed peripheral Integrated Circuits (ICs), processors and microcontrollers. But silicon today has changed...

Certus Semiconductor’s I/O libraries for TSMC’s 22nm ultra-low leakage (22ULL) and 22nm ultra-low power (22ULP) technologies offer robust, high-performance solutions tailored to a wide range of SoC designs — from ultra-low power IoT nodes to demanding consumer and automotive systems. Whether you need low leakage, high drive strength, or analog compatibility, our production-proven IP covers it all.