MIPI RFFE Slave IP Core

The MIPI RFFE Slave controller IP is a optimized and technology and PHY agnostic implementation of the MIPI RFFE v.3.1 standard t…

Overview

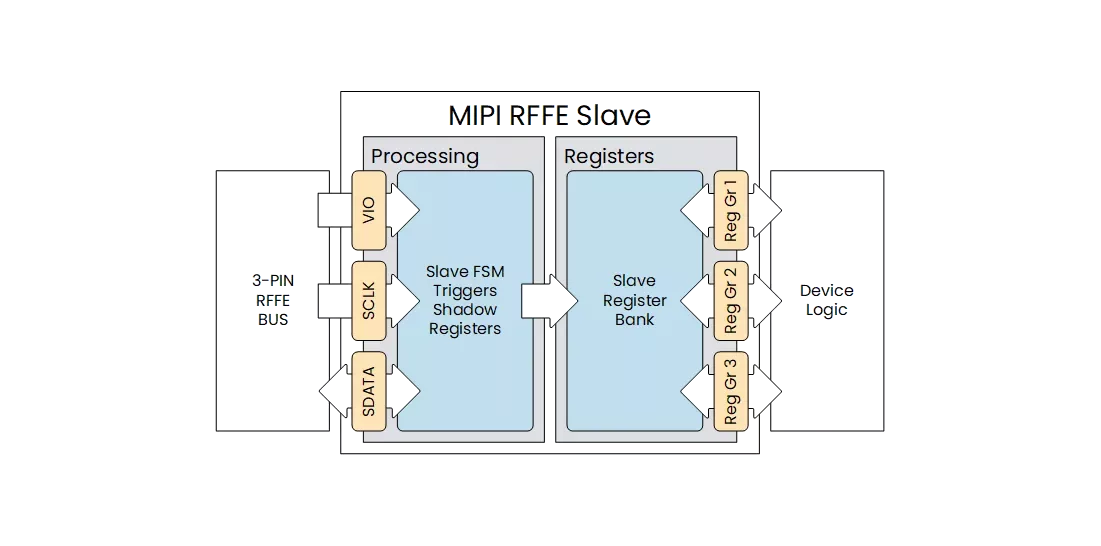

The MIPI RFFE Slave controller IP is a highly optimized and technology and PHY agnostic implementation of the MIPI RFFE v.3.1 standard targeting both ASIC and FPGA technologies. This IP is used to connect a digital RFIC to RF front end components, like Power Amplifiers (PA), Low-Noise Amplifiers (LNA), filters, switches, power management modules, Antenna Turner and Sensors,which are considered RFFE Slaves. This MIPI RFFE Slave IP is backward compatible with MIPI RFFE components version 3.0, 2.1, 2.0 and 1.0.

The IP-core has been rigorously tested in System Verilog random regression environment.

The MIPI RFFE Slave IP core is a highly optimized Silicon Agnostic implementation of the MIPI RFFE protocol version 3.1, used to connect a digital RFIC to RF Front end components, targeting both ASIC and FPGA’s. It delivers all features of the standard and allows for great configurability of features.

The IP support a configurable amount of slave device registers in 3 separate groups. Making it possible to build the most complex of systems.

Trigger remapping, and timed trigger operation, allow to make efficient use of the slave registers via the shadow register mechanism, coordinating the register value changes to specific points in time.

Trigger remapping, and timed trigger operation, allow to make efficient use of the slave registers via the shadow register mechanism, coordinating the register value changes to specific points in time.

Key features

- Delivering Performance

- Fully compliant with MIPI RFFE v3.1 Specification

- Supports all RFFE Slave commands

- Support Standard, Timed and Mappable Triggers

- Supports all USID Prgramming procedures: 1, 2 and 3

- Supports wide range of clock frequencies up to maximum 52 MHz

- Configurable number of type of registers

- Easy to use

- Solid documentation including integration guide

- Easy to use RTL test environment

- No special software required

- Strong engineering support for bring-up

- Robust

- UVM based Verification

- Lint/CDC checked

- Silicon Agnostic

- Targeting both ASICs and FPGAs

Block Diagram

What’s Included?

- The IP Core can be delivered in Source code or Encrypted format.

- The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual, Release Note and Quick Start Guide.

- Simulation Environment, including Simple

- Testbed, Test case, Test Script.

- Basic RTL Test Bench

- Synthesis Scripts

- Synopsys Lint and CDC Waivers

- Synopsys CDC SGDC Files

- Synopsys Constraint Files

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI RFFE IP core

Frequently asked questions about MIPI RFFE IP cores

What is MIPI RFFE Slave IP Core?

MIPI RFFE Slave IP Core is a MIPI RFFE IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this MIPI RFFE?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI RFFE IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.