RFFE Slave IP Core

Mobile radio communication is trending towards complex multi-radio systems comprising several transceivers.

Overview

Mobile radio communication is trending towards complex multi-radio systems comprising several transceivers. Arasan supports the latest MIPI RFFE standard v3.0 controller IP. The MIPI RFFE bus is a 2-wire serial interface that utilizes a bus frequency of up to 52 MHz and timing accurate trigger mechanisms to allow control of timing-critical functions. It is used to connect a digital RFIC to RF front end components, like Power Amplifiers, Low-Noise Amplifiers, and Antenna Sensors, which are considered RFFE Slaves.

One key component of MIPI RFFE v3.0 controller IP was to retain backward-compatibility, especially for MIPI RFFE v2.0 and v1.0 Slave devices. This requirement enables MIPI RFFE v2.0 and v1.0 Slave devices to function properly in a MIPI RFFE v3.0 controller IP system. Of course, such MIPI RFFE v1.0 and v2.0 -compliant Slave devices in a MIPI RFFE v3.0 controller IP system are limited to their MIPI RFFE v1.0 and v2.0 functionality respectively.

Arasan’s MIPI RFFE v3.0 IP compatible Slave device implements the following new optional features:

- Support for Extended Triggers which is referred to as Block B Triggers

- Support for Timed Triggers

- Support for Mappable Triggers

- Additional ports may have to be added depending upon the features supported

The MIPI RFFE Slave IP core typically resides in the RFIC in a mobile platform, and utilizes the RFFE bus to identify, program, and monitor the registers in RF front end Slave devices through programmed IO. It is designed to support existing standards such as LTE, UMTS, HSPA and EGPRS, and is usable in configurations ranging from single Master/single Slave to multi-Master/multi-Slave.

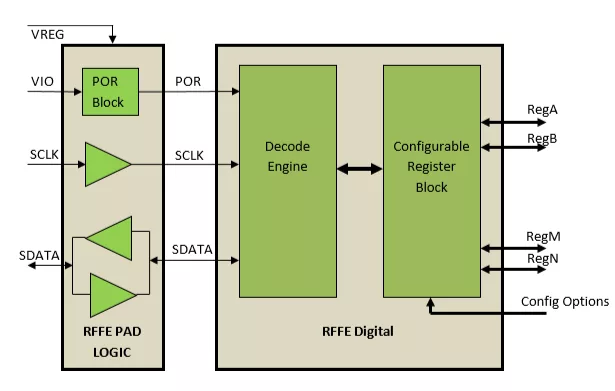

The MIPI RFFE Slave V3.0 IP Core resides in each RF front end component. At a minimum, Arasan delivers MIPI RFFE Slave in RTL form. Physical designs of the complete MIPI RFFE Slave, including the Pad Logic block for CLK and DATA as shown below, can be provided upon request.

Key features

- Compliant with MIPI’s RFFE specification Rev 3.0

- Small silicon footprint

- Scalable Implementation

- Up to 15 Devices can be connected per Bus

- Low pin count on Interface side (SCLK and SDATA)

- Low EMI

- Low power consumption

- Timing accurate Trigger mechanisms

- Highly configurable

- Relatively High speed CLK of 52Mhz

- Extension of the Manufacturer ID Bit Field to 12 bits

- Addition of Longer Reach RFFE Bus Length up to 45cm from 15cm

- Introduction of Masked Write Command Sequence

- Added 8 Extended Triggers along with 3 standard Triggers

- sRead / BPC Issue Resolution

- Master to/from Slave data payload sizes in Command Sequences may be from 1 to 16 bytes

- Master to/from Master data payload sizes in Command Sequences may be from 1 to 256 bytes

- Additional Register Space was added, (Extended Long) Reserved Registers for Future Use (0XFE00-0XFFFF)

Block Diagram

Benefits

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

- Functionality ensured with comprehensive verification

- Premier direct support from Arasan IP core designers

What’s Included?

- RTL Source Files

- Test Bench with BFM’s

- Full test cases list

- Scripts for Synthesis, Simulation, LEC

- GDS-‐II Database (Optional)

- LVS Netlist (Optional)

- Physical Abstract Models (LEF) (Optional)

- Timing Models (LIB) (Optional)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI RFFE IP core

Frequently asked questions about MIPI RFFE IP cores

What is RFFE Slave IP Core?

RFFE Slave IP Core is a MIPI RFFE IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this MIPI RFFE?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI RFFE IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.