LPDDR5X/5/4X/4 PHY for 16nm

The LPDDR5X/5/4X/4 combo PHY IP features a state-of-art mixed-signal architecture that addresses the challenges of DRAM integrati…

Overview

The LPDDR5X/5/4X/4 combo PHY IP features a state-of-art mixed-signal architecture that addresses the challenges of DRAM integration in high-performance and low-power environments. This architecture enables LPDDR5/4 combo PHY IP to overcome issues with long-term impedance drift and clock phase drift, allowing impedance and clock phase updates without interrupting data traffic. The programmable timing at the OPHY boundary combines flexibility with analog precision, resulting in low read/write latency between OMC and the LPDDR5/4 DRAM without sacrificing performance.

The LPDDR5X/5/4X/4 combo PHY IP was designed with subsystem and system-level considerations in mind. Built-in power management logic and advanced PLL design allow aggressive power state management and optimal system power usage. At the system level, the LPDDR5X/5/4X/4 combo PHY IP was designed to minimize package substrate layer and PCB layer requirements, enabling usage in cost-sensitive applications and application processors.

OPENEDGES Technology, Inc. (OPENEDGES) is a premier provider of memory subsystem IPs for the semiconductor industry. The company offers a wide range of state-of-the-art solutions, including DDR memory controllers, DDR PHY, NoC interconnect, and NPU IPs that are widely adopted by customers worldwide. Their IPs comply with JEDEC standards, including LPDDR5X/5/4X/4/3, DDR5/4/3, GDDR6, and HBM3, ensuring their compatibility with the latest DDR technology trends. OPENEDGES' IPs are tightly combined to bring synergy for high performance and low latency when used together or even in a single use. OPENEDGES' integrated IP solutions are market and silicon-proven, featuring advanced architectures and proprietary technologies that enable customers to shorten their design and verification processes.

Key features

- Compliant with JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports up to 4 ranks

- Multiple frequency states

- PHY independent training and calibration

- Firmware based training

- Hardware or Firmware based retraining

- Proprietary microcontroller with custom ISA

- Multiple DFICLK: CK ratios and DFICLK:CK: WCK ratio

- Tx and Rx channel equalization

- Voltage and temperature tracking of timing and impedance control circuit

- Flexible floor planning/bump mapping

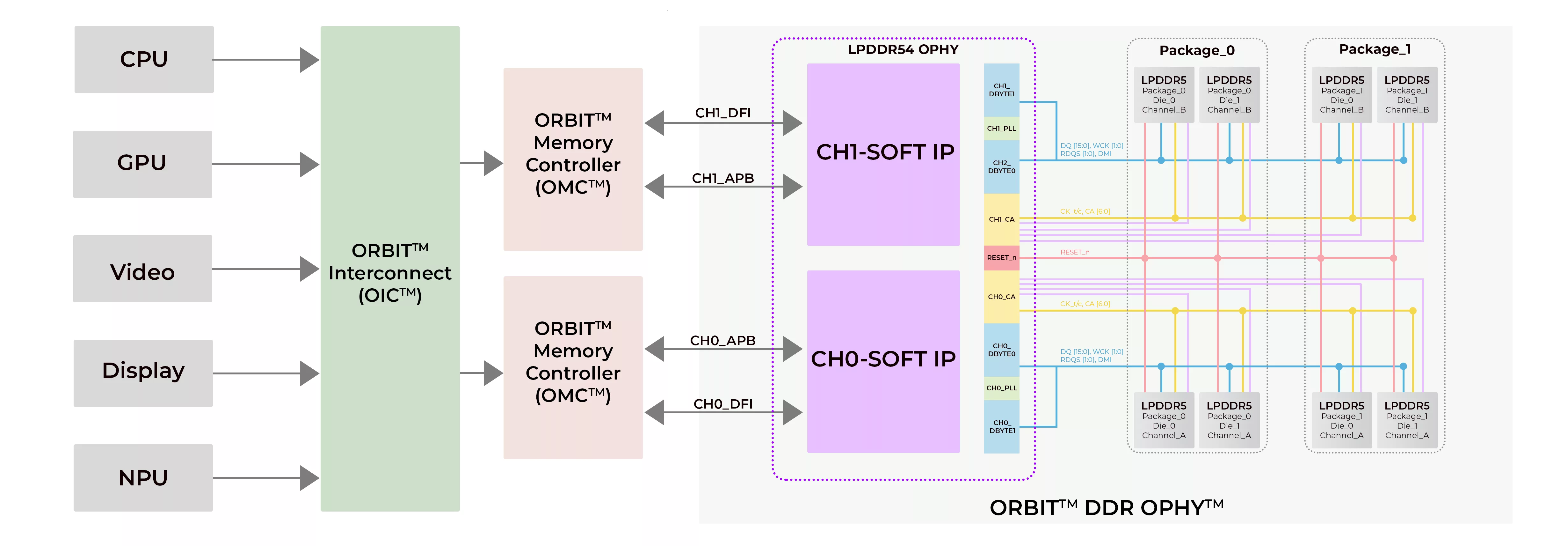

Block Diagram

Benefits

- Configurability with Flexible Applications

- Cost-effective with minimal package substrate/PCB layer requirements

- High Performance

- Firmware-based training / ultra-fast fractional training

- Fast switching between FSPs

- Programmable PHY boundary timing providing low read/write latency

- Maximize capacity with channel equalization at the multi rank

- Low Power scheme using power-saving mode and multiple voltage domains

Applications

- Consumer edge devices

- Digital set-top-boxes

- TVs

- SSD controllers

- Application processors

What’s Included?

- Hard & Soft IP

- GDSII, LEF, LVS, timing models, etc.

- Verilog behavior models and encrypted RTL

- Synthesis and STA constraints

- Example test benches

- Documentation

- PHY Technical Reference Manual

- Implementation, package, and PCB design guidelines

- Test and characterization guidelines

- Physical verification reports

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about LPDDR IP core

LPDDR flash: A memory optimized for automotive systems

A New Generation of LPDDR

Enabling Memory Choice for Modern AI Systems: Tenstorrent and Rambus Deliver Flexible, Power-Efficient Solutions

SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

On-Device AI Semiconductors & High-speed Interconnects in the Physical AI era

Frequently asked questions about LPDDR IP

What is LPDDR5X/5/4X/4 PHY for 16nm?

LPDDR5X/5/4X/4 PHY for 16nm is a LPDDR IP core from OPENEDGES Technology, Inc. listed on Semi IP Hub.

How should engineers evaluate this LPDDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this LPDDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.