Interlaken Look-Aside Intel® FPGA IP

Interlaken Look-Aside is a scalable protocol that allows interoperability between a datapath device and a look-aside coprocessor …

Overview

Interlaken Look-Aside is a scalable protocol that allows interoperability between a datapath device and a look-aside coprocessor for short, transaction-related transfers. A look-aside coprocessor is connected "to the side" of the datapath, and is not in-line of the main datapath of the switch, router, or other networking device. Interlaken Look-Aside is not directly compatible with Interlaken and can be considered a different operational mode.

Interlaken Look-Aside Interconnect Protocol

The Interlaken Look-Aside IP core is suited for coprocessing packet classification typically used for networking applications such as: Quality of service routing, traffic profiling, and firewall functions. The IP's low-latency packet interface, coupled with its efficient data processing capability, enables a high degree of design scalability for emerging network applications.

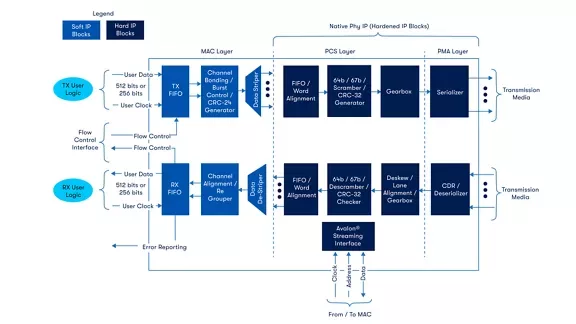

This IP core includes Intel's technology-leading transceivers:

- Physical medium attachment (PMA)

- Physical coding sublayer (PCS)

- Media access control (MAC) layers.

The PCS and PMA layers are hardened within the Stratix® 10, Arria® 10, Stratix V, and Arria V FPGAs.

Intel has been a part of the Interlaken Alliance since its inception in 2007 and continues to innovate with new protocol features to provide customers with robust and easy-to-implement Interlaken Look-Aside IP solutions. The Interlaken Look-Aside Intel FPGA IP core offers a wide range of bandwidths up to 300G.

The Interlaken Look-Aside IP core is Interlaken Look-Aside Protocol Definition v1.1 compliant and allows system developers to eliminate the computational bottlenecks associated with older, packet classification methods. Intel also offers customized Interlaken Look-Aside IP solutions. For more information, please contact your local sales representative.

Intel and Cavium Team Up to Provide Pre-verified Packet Classification Solution

The Interlaken Look-Aside Intel FPGA IP core on a Stratix® V FPGA with Cavium’s NEURON Search Processor provides customers a proven packet classification solution that can easily be implemented on any networking or data center platform.

To further simplify our customers’ decision-making process, Intel and Cavium have generated an interoperability report that details the various interoperability modes and performance metrics that can be achieved with this complete, high-performance chipset. Contact your sales person for a copy of this report.

Intel and Cavium Connectivity System Overview

The Interlaken Look-Aside Intel FPGA IP core on a Stratix® V FPGA with Cavium’s NEURON Search Processor provides customers a proven packet classification solution that can easily be implemented on any networking or data center platform.

To further simplify our customers’ decision-making process, Intel and Cavium have generated an interoperability report that details the various interoperability modes and performance metrics that can be achieved with this complete, high-performance chipset. Contact your sales person for a copy of this report.

Key features

- Data rate selection up to 25 Gbps

- Multi-lane configuration up to 24 lanes

- Packet mode support

- Low-latency transmit and receive datapaths

- BurstShort support: 8 bytes or higher

- Up to two logical channels

- In-band flow control

- Fully integrated IP (MAC, PCS, and PMA layers)

- Tunable pre-emphasis and equalization settings

- Custom IP deliveries available to optimize for various application needs

- Available through the IP catalog in the Quartus® Prime Pro Edition software

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Interlaken IP core

Why Interlaken is a great choice for architecting chip to chip communications in AI chips

Interlaken: the ideal high-speed chip-to-chip interface

How to design an Interlaken to SPI-4.2 bridge

The Benefits of a Multi-Protocol PMA

Multi-Channel Multi-Rate (MCMR) Forward Error Correction (FEC) - IP for High Speed Networking Applications

Frequently asked questions about Interlaken IP cores

What is Interlaken Look-Aside Intel® FPGA IP?

Interlaken Look-Aside Intel® FPGA IP is a Interlaken IP core from Altera listed on Semi IP Hub.

How should engineers evaluate this Interlaken?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Interlaken IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.