Interlaken Controller

World-class, industry-, scalable, silicon- and PHY-agnostic IP core with 116 Gbps line rate, interoperability tested with Serdes …

Overview

World-class, industry-leading, highly scalable, silicon- and PHY-agnostic IP core with 116 Gbps line rate, interoperability tested with leading Serdes providers

Interlaken is a scalable chip-to-chip protocol, which ensures the integrity of reliable data transfer and managing data flows to prevent data overload. The Interlaken IP core is a highly optimized silicon and PHY agnostic implementation of the Interlaken Protocol version 1.2 targeting both ASICs and FPGAs. Our Interlaken controller supports up to 2.6 Tbps high-bandwidth performance and comes with an integrated Media Access layer.

The Interlaken Controller can be widely used in chip-to-chip transfers, it has an extensive feature-set available and allows scalability in number of logic channels (up to 2048), lanes (up to 48) and lane speed (up to 56 Gbps). The IP core is heavily tested in SystemVerilog random regression environment

The Interlaken IP core is a highly optimized silicon and PHY agnostic implementation of the Interlaken Protocol version 1.2 targeting both ASICs and FPGAs. It delivers all features of the standard and includes Retransmission and RS FEC Standard extensions.

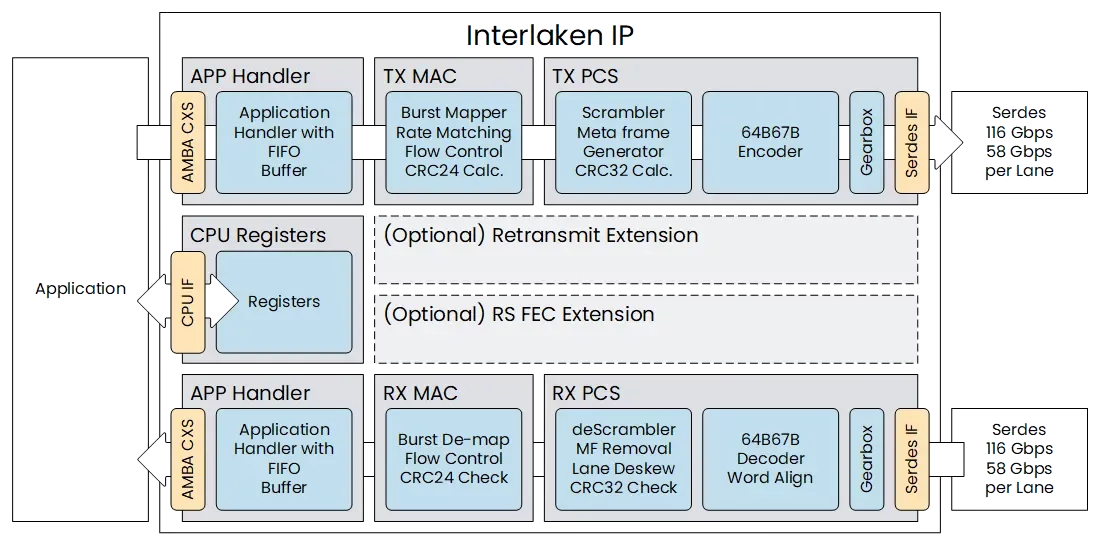

The solution consists of combined TX and RX data paths with PCS, MAC and Protocol layers included. In Band Flow control over the data lanes and Out of Band Flow control over a separate interface are available.

Error recovery is made possible via the Retransmit extension. Error correction and PAM 4 encoding with Line rates up to 116Gbps is made possible with the RS FEC extension.

Key features

- MAC layer with fast AMBA CXS interface

- PCS layer highly configurable with up to 48 lanes

- Multi-lane configurations, up to 48 lanes

- 64B 67B encoding/decoding supported

- Supports up to 2048 logic channels

- Programmable Meta Frame lengths

- Programmable Interlaken Bursts: Short from 32 and Max up to 1024 Bytes

- Flow control support

- Mode of operation: Packet mode and Interleave mode supported

- Re-transmit

- Interlaken Dual Calendar

- Look-Aside

- FEC support

Block Diagram

Benefits

- Test Environment

- Interlaken IP is tested in a UVM based regression environment for full functional coverage

- Silicon Agnostic

- Designed in Verilog and targeting both ASIC and FPGA technologies

- Interoperability Tested

- Interlaken IP is interoperability tested with leading PHY providers and other market available Interlaken solutions

- PHY Integration

- PHY Integration support with additional hours or off the shelf PHY integration package for quick and efficient deployment

- Active Support

- All support is actively provided by engineers directly

What’s Included?

- The IP Core can be delivered in Source code or Encrypted format.

- The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual, Release Note and Quick Start Guide.

- Simulation Environment, including Simple Testbed, Test case, Test Script.

- Programming Register Specification.

- Timing Constraints in Synopsys SDC format.

- Access to support system and direct support from Chip Interfaces Engineers.

- Test Report , Synopsys SGDC Files and Synopsys Lint, CDC and Waivers available on request

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Interlaken IP core

Why Interlaken is a great choice for architecting chip to chip communications in AI chips

Interlaken: the ideal high-speed chip-to-chip interface

How to design an Interlaken to SPI-4.2 bridge

The Benefits of a Multi-Protocol PMA

Multi-Channel Multi-Rate (MCMR) Forward Error Correction (FEC) - IP for High Speed Networking Applications

Frequently asked questions about Interlaken IP cores

What is Interlaken Controller?

Interlaken Controller is a Interlaken IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this Interlaken?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Interlaken IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.